## How to report and benchmark emerging field-effect transistors

Zhihui Cheng <sup>1,2</sup> <sup>∞</sup>, Chin-Sheng Pang <sup>2</sup>, Peiqi Wang<sup>3</sup>, Son T. Le<sup>1,4</sup>, Yanqing Wu <sup>5</sup>, Davood Shahrjerdi <sup>6,7</sup>, Iuliana Radu<sup>8</sup>, Max C. Lemme<sup>9,10</sup>, Lian-Mao Peng <sup>11</sup>, Xiangfeng Duan <sup>3</sup>, Zhihong Chen <sup>2</sup>, Joerg Appenzeller <sup>2</sup>, Steven J. Koester <sup>12</sup>, Eric Pop <sup>13</sup>, Aaron D. Franklin <sup>14,15</sup> <sup>∞</sup> and Curt A. Richter <sup>1∞</sup>

The use of organic, oxide and low-dimensional materials in field-effect transistors has now been studied for decades. However, properly reporting and comparing device performance remains challenging due to the interdependency of multiple device parameters. The interdisciplinarity of this research community has also led to a lack of consistent reporting and benchmarking guidelines. Here we propose guidelines for reporting and benchmarking key field-effect transistor parameters and performance metrics. We provide an example of this reporting and benchmarking process using a two-dimensional semiconductor field-effect transistor. Our guidelines should help promote an improved approach for assessing device performance in emerging field-effect transistors, helping the field to progress in a more consistent and meaningful way.

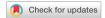

esearch into field-effect transistors (FETs) based on emerging nanomaterials—including carbon nanotubes<sup>1,2</sup>, graphene<sup>3</sup>, phosphorene<sup>4</sup>, silicene<sup>5</sup>, tellurene<sup>6</sup>, transition metal dichalcogenides<sup>7-9</sup>, organic semiconductors<sup>10,11</sup> and ultrathin metal oxides<sup>12</sup>—is thriving. Such studies allow the fundamental properties of the materials to be explored, and may lead to the development of various commercial applications. However, effectively and uniformly assessing the performance of emergent FETs is difficult due to the dependence of performance metrics on unique aspects of the device structure (Fig. 1a)<sup>13</sup>.

The structural parameters that influence device performance include channel length  $(L_{ch})$  and contact length  $(L_c)$ , gate insulator thickness ( $t_{\rm ins}$ ) and permittivity ( $\epsilon_{\rm ins}$ ), contact metal types, the thickness of the channel material ( $t_{ch}$ ) and the gating scheme (for example, top, bottom, gate-all-around, multi-channel). Performance metrics include on current  $(I_{on})$ , off current  $(I_{off})$ , the  $I_{on}/I_{off}$  ratio, contact resistance  $(R_c)$ , transconductance  $(g_m)$ , subthreshold swing (SS), channel mobilities and drain-induced barrier lowering (DIBL). Although the different studies reported in the literature often include some of these benchmarking figures, they struggle to capture the myriad variables, making comparisons inaccurate or even biased at times. In addition, the emerging device community consists of researchers from disparate disciplines—including electrical engineering, chemistry, materials science and physics—which also makes consistent reporting and benchmarking challenging. In this Perspective we examine the challenges involved in assessing the operation and performance of FETs based on emerging materials, and provide guidelines on how to report and benchmark the devices.

## Field-effect transistor structure and key parameters

In a FET, the structural parameters determine the electric fields and the eventual device performance (Fig. 1a). The subthreshold, transfer and output characteristics presented in Fig. 1b–d are the most common I-V (current–voltage) curves to capture device performance. Plotting the log of the drain current  $(I_{\rm D})$  as a function of gate–source voltage  $(V_{\rm GS})$  highlights the subthreshold (that is, off state) device behaviour. In contrast, transfer characteristics plot  $I_{\rm D}$  versus  $V_{\rm GS}$  on a linear scale and emphasize the device behaviour after  $V_{\rm GS}$  exceeds the threshold voltage  $(V_{\rm T})$ , where the device is in the on state. Ideally, the gate leakage current  $(I_{\rm G})$  versus  $V_{\rm GS}$  should be plotted on the subthreshold plot as well.

The  $I_D$ - $V_{GS}$  sweeps in Fig. 1b,c should be conducted at both 'small' and 'high' drain-source voltage ( $V_{\rm DS}$ ) values to characterize device operation in both the linear and saturation regimes. We note that the small  $V_{\rm DS}$  value should be sufficiently small to ensure linear-regime operation, but greater than  $\sim 2k_{\rm B}T$  (where  $k_{\rm B}$ is the Boltzmann constant and T is the absolute temperature, that is, ~50 mV at room temperature) to ensure that the subthreshold behaviour (here, in particular, DIBL,  $\partial V_T/\partial V_{DS}$ ) is not misinterpreted due to thermal injection of carriers from the drain. These curves enable easy extraction of DIBL to demonstrate how  $V_{DS}$ impacts  $V_T$ . The transfer characteristics should be acquired with forwards and backwards sweeps, checking for the presence of any hysteresis due to charge trapping<sup>14</sup>. When comparing the hysteresis from different devices, precise measurement conditions such as sweep rates, hold times and maximum bias voltages should be listed, as these parameters influence hysteresis. If hysteresis exists, it

Nanoscale Device Characterization Division, National Institute of Standards and Technology, Gaithersburg, MD, USA. <sup>2</sup>Department of Electrical and Computer Engineering, Purdue University, West Lafayette, IN, USA. <sup>3</sup>Department of Chemistry and Biochemistry, University of California, Los Angeles, Los Angeles, CA, USA. <sup>4</sup>Theiss Research, La Jolla, CA, USA. <sup>5</sup>School of Integrated Circuits, Peking University, Beijing, China. <sup>6</sup>Electrical and Computer Engineering, New York University, Brooklyn, NY, USA. <sup>7</sup>Center for Quantum Phenomena, Physics Department, New York University, New York, NY, USA. <sup>8</sup>IMEC, Leuven, Belgium. <sup>9</sup>RWTH Aachen University, Chair of Electronic Devices, Aachen, Germany. <sup>10</sup>AMO GmbH, Advanced Microelectronic Center Aachen, Aachen, Germany. <sup>11</sup>Key Laboratory for the Physics and Chemistry of Nanodevices and Center for Carbon-based Electronics, Department of Electronics, Peking University, Beijing, China. <sup>12</sup>Department of Electrical and Computer Engineering, University of Minnesota, Minneapolis, MN, USA. <sup>13</sup>Department of Electrical Engineering, Stanford University, Stanford, CA, USA. <sup>14</sup>Department of Electrical and Computer Engineering, Duke University, Durham, NC, USA. <sup>15</sup>Department of Chemistry, Duke University, Durham, NC, USA. <sup>16</sup>Department of Chemistry, Duke University, Durham, NC, USA. <sup>18</sup>Department o

**Fig. 1 Basic device structure and electrical characteristics. a**, Diagram of a typical nanomaterial-based n-type FET, highlighting the structure parameters and electric fields. TMD, transition metal dichalcogenide;  $W_{chv}$  channel width;  $L_{chv}$  channel length;  $L_{cv}$  contact length;  $t_{chv}$  channel material thickness;  $t_{insr}$  gate insulator thickness;  $E_{gatev}$  vertical electric field at the source end;  $E_{chv}$  the channel electric field between source and drain. **b,c**, Subthreshold (**b**) and transfer (**c**) ( $I_D$ – $V_{CS}$ ) curves of an n-type FET under different  $V_{DS}$  voltages. Representative curves are shown for a single sweep in **b**, but forwards and backwards sweeps of  $V_{CS}$  should be collected to determine hysteresis, as shown in **c**. The gate leakage current is also shown in **b**. **d**, Output ( $I_D$ – $V_{DS}$ ) curves of the device, with the three main operation regimes labelled  $^{16}$ .  $V_{CS}$  is sweept from low to high in steps of  $\Delta V_{CS}$ ,  $v_{sat}$  is the saturation velocity of carriers in the channel material.  $I_{sat}$  scales as  $V_{OV}^2$  in the classical pinch-off regime, but only linearly with  $V_{OV}$  when the velocity saturates. Self-heating could render this increase even sublinear  $I_{SS}^{16,54}$ . Note that  $V_{DS}$  is the supply voltage for the transistor (that is, the target maximum voltage of operation for both  $V_{DS}$  and  $V_{CS}^2$ ).

should be accounted for in the analysis of  $V_{\rm T}$  uncertainty and other device parameters that depend on  $V_{\rm T}$ .

In the output characteristics (Fig. 1d), three main operation regimes are highlighted. The linear regime is characterized by the linear increase of  $I_{\rm D}$  with both  $V_{\rm DS}$  and  $V_{\rm GS}$ . After  $V_{\rm DS}$  surpasses the overdrive voltage ( $V_{\rm OV}\!=\!V_{\rm GS}\!-\!V_{\rm T\!P}$  for n-channel FETs),  $I_{\rm D}$  starts to saturate to  $I_{\rm sat}$ , which could (based on the classical FET model  $^{15}$ ) increase quadratically with  $V_{\rm OV}$  in the pinch-off regime and linearly with  $V_{\rm OV}$  in the velocity saturation regime  $^{16}$ . Note that the linear regime may present as nonlinear (often exponential) in the event of poor carrier injection at the contacts, such as from large Schottky barriers.

Multiple performance parameters can be extracted from the I-Vcurves in Fig. 1b-d. The most important performance metrics are the currents, which must be reported normalized by the channel width,  $W_{ch}$  (for example, in units of  $\mu A \mu m^{-1}$ ). For one-dimensional (1D) or quasi-1D devices, it is common to first report the current per carbon nanotube (CNT)/nanowire/nanosheet stack. The current can then be normalized to units of μA μm<sup>-1</sup> by considering the expected channel density and pitch of the channel material (for example, 10 µA per CNT with 50 CNTs µm<sup>-1</sup>, giving 500 µA µm<sup>-1</sup>), because the aerial footprint of the device is a critical aspect of performance. When extracting  $I_{\rm on}$  and  $I_{\rm off}$  from these I-V curves, in a simplified scenario,  $I_{\rm off}$  is the  $I_{\rm D}$  measured at  $V_{\rm GS}\!=\!0$  and  $V_{\rm DS}\!=\!V_{\rm DD}$ , whereas  $I_{\text{on}}$  is the  $I_{\text{D}}$  measured at  $V_{\text{GS}} = V_{\text{DS}} = V_{\text{DD}}$ . Here,  $V_{\text{DD}}$  is the voltage that would be supplied to operate the transistors. (For mainstream silicon technology,  $V_{\rm DD}$  dropped to 1 V near 2010 and to 0.7 V in recent years<sup>17</sup>.) For modern technologies, the exact value of  $V_{\rm DD}$

depends on the application. For example, if the emergent transistor is used as an access transistor in a dynamic random-access memory (DRAM), then its  $V_{\rm DD}$  will be a small value to ensure linear-regime operation in the on state. Reported emergent devices often do not have threshold voltages tuned such that  $V_{\rm GS}\!=\!0$  is a sensible off state; additionally, there is often not a well-defined  $V_{\rm DD}$  value due to the wide variety of device structural parameters. We hence suggest extracting the maximum and minimum  $I_{\rm D}$  ( $I_{\rm max}$  and  $I_{\rm min}$ ) from a typical subthreshold curve and reporting the  $I_{\rm max}/I_{\rm min}$  ratios when  $V_{\rm DS}$  is biased in both the linear and saturation regimes. A more detailed description on reporting and benchmarking  $I_{\rm max}/I_{\rm min}$  is provided in Supplementary Note 1.

When reporting the  $I_{\text{sat}}$  of a device, it is necessary to note the carrier density n at which the  $I_{\rm sat}$  is extracted. Ideally, the Hall effect is used to measure the carrier density for the channel material, but for most researchers in the FET community, more accessible approaches are needed that do not require specially designed test structures. In the linear regime, the average carrier density can be estimated as  $n \approx C_{\text{ins}} (V_{\text{OV}} - V_{\text{DS}}/2)/q$ , where  $C_{\text{ins}}$  is the gate insulator capacitance and q is the elementary charge; however, in the saturation regime, the depletion region in the channel complicates the estimation. The carrier density near the source side is the same for both the linear and saturation regimes. For convenience and simplicity, we recommend clearly labelling the carrier density near the source as  $n_s$  (= $C_{ins}V_{OV}/q$ ) and using this value for both operation regimes. To determine  $V_{OV}$ ,  $V_{T}$  is usually estimated using extrapolation in the linear portion of the transfer curve, as listed in Table 1. Other methods, such as constant-current<sup>18</sup>, Y-function

PERSPECTIVE NATURE ELECTRONICS

| Name                                                                | Characteristics                                                                                                                                                     | Additional details                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Structural parameters                                               | Contact length, $L_{\rm c}$<br>Channel length, $L_{\rm ch}$<br>Channel width, $W_{\rm ch}$<br>Insulator thickness, $t_{\rm ins}$<br>Channel thickness, $t_{\rm ch}$ | Specify contact and gating geometry/materials; include high-resolution electron microscopy evidence when reporting sub-20-nm dimensions (especially for $L_{\rm c}$ and $L_{\rm ch}$ )                                                                                                                                                                                                  |

| Insulator capacitance, $C_{\rm ins}$                                | Capacitance-voltage or capacitance-frequency                                                                                                                        | Measured $C_{\rm ins}$ is more accurate than estimating $\epsilon_{\rm ins}$ especially when a high- $k$ insulator is used                                                                                                                                                                                                                                                              |

| Threshold voltage, $V_{\rm T}$ , and hysteresis, $\Delta V_{\rm T}$ | Extrapolation in the linear portion of the transfer curve <sup>18</sup>                                                                                             | <ul> <li>I<sub>D</sub>-V<sub>GS</sub> should have forwards and backwards sweeps</li> <li>Consider V<sub>T</sub> uncertainty due to hysteresis (charge trapping), the dependence of V<sub>DS</sub> and I-V sweeps (Supplementary Note 2)</li> </ul>                                                                                                                                      |

| Drain current in saturation regime, $I_{\rm sat}$                   | $I_{\rm D}$ - $V_{\rm DS}$ (saturation regime)                                                                                                                      | <ul> <li>Sweep I<sub>D</sub>-V<sub>DS</sub> to the saturation regime</li> <li>Specify carrier density where I<sub>sat</sub> is extracted</li> <li>Normalized by channel width</li> </ul>                                                                                                                                                                                                |

| Contact resistance, $R_{\rm c}$                                     | Transfer length method (TLM) <sup>22</sup> (Supplementary Note 3)                                                                                                   | <ul> <li>Linear regime (small V<sub>DS</sub>)</li> <li>Specify carrier density n<sub>S</sub> or plot R<sub>c</sub> versus n<sub>S</sub></li> <li>TLM should have at least four channels and include at least one each of contact and channel resistance-dominated devices</li> </ul>                                                                                                    |

| Conductivity mobility, $\mu_{\rm con}$                              | $\frac{1}{qn_5R_{\rm sh}}$                                                                                                                                          | <ul> <li>R<sub>sh</sub> is extracted from the slope of TLM plots or from four-probe measurements<sup>21</sup> (units: Ω□<sup>-1</sup>)</li> <li>Carrier density near the source: n<sub>S</sub> ≈ C<sub>ins</sub>V<sub>OV</sub>/q</li> <li>Mobility from R<sub>sh</sub> = (qn<sub>S</sub>μ)<sup>-1</sup></li> <li>Plot mobility versus n<sub>S</sub> to show field dependence</li> </ul> |

| Transconductance, $g_{\scriptscriptstyle \rm m}$                    | Transfer or output curves $g_{\rm m}=rac{\partial l_{ m D}}{\partial V_{ m GS}}$ at certain $V_{ m DS}$                                                            | Specify $g_{\scriptscriptstyle \mathrm{m}}$ (linear) or $g_{\scriptscriptstyle \mathrm{m}}$ (saturation)                                                                                                                                                                                                                                                                                |

| Subthreshold swing (SS)                                             | Subthreshold curves (inverse slope in mV dec $^{-1}$ below $V_{\rm T}$ )                                                                                            | <ul> <li>SS depends on C<sub>ins</sub> and interface trap capacitance C<sub>it</sub></li> <li>Plot SS versus log<sub>10</sub>(I<sub>D</sub>)</li> </ul>                                                                                                                                                                                                                                 |

| $I_{\rm on}/I_{\rm off}$                                            | Subthreshold curves at saturation regime, $V_{DS} = V_{DS}$ (sat)                                                                                                   | <ul> <li>Report I<sub>max</sub>/I<sub>min</sub> as an alternative along with the n<sub>S</sub> range</li> <li>Plot I<sub>G</sub> versus V<sub>GS</sub> to show leakage current</li> </ul>                                                                                                                                                                                               |

| DIBL                                                                | $\Delta V_{\text{T}}/\Delta V_{\text{DS}}$ from transfer curves                                                                                                     | Key for short-channel devices                                                                                                                                                                                                                                                                                                                                                           |

methods<sup>19,20</sup> and four-probe measurements<sup>21</sup>, can be used to cross-check the linear extraction of  $V_{\rm T}$  and reduce the variation when estimating  $n_{\rm S}$ . More discussion regarding  $V_{\rm T}$  extraction is given in Supplementary Note 2.

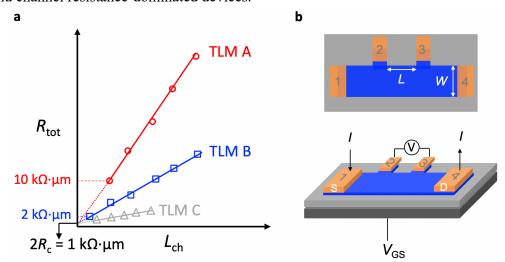

In addition to  $I_D$ ,  $R_c$  is also essential to represent device performance. The transfer length method (TLM) is the most commonly used approach for extracting  $R_c$ , along with the sheet resistance,  $R_{\rm sh}$ , of the channel (in units of  $\Omega \square^{-1}$ )<sup>22</sup>. The TLM approach requires a series of FETs with different channel lengths and consistent contact and gating configurations. It entails plotting the total resistance of each device versus  $L_{ch}$  at a given  $n_s$ , allowing  $R_c$  to be extracted as the extrapolated y-axis intercept from a linear fit to the data points. Typically, the  $V_{DS}$  for calculating the total resistance is the small  $V_{\rm DS}$  used in Fig. 1b to ensure linear-regime operation. The channel lengths in the TLM should range from short (where the total resistance is dominated by  $R_c$ ) to long (dominated by channel resistance  $R_{\rm ch} = R_{\rm tot} - 2R_{\rm c}$  or  $R_{\rm sh}L_{\rm ch}$ ) where the actual short and long channel lengths will depend on the relationship between the channel resistance and the contact resistance. A more detailed discussion on extracting R<sub>c</sub> and other considerations using TLM data is provided in Supplementary Note 3.

Another frequently reported parameter is the carrier mobility of the channel material. Among various forms of mobility, the field-effect mobility  $\mu_{\rm FE} = L_{\rm ch} g_{\rm m}/(W_{\rm ch} C_{\rm ins} V_{\rm DS})$  is often used. However,  $\mu_{\rm FE}$  can be underestimated<sup>20,23</sup> or overestimated<sup>21,24,25</sup> relative to the drift mobility of the channel material depending on the details of  $V_{\rm DS}$ ,  $V_{\rm GS}$ ,  $R_{\rm c}$ ,  $L_{\rm ch}$ , and gate capacitance. In particular, gated contact effects can significantly affect mobility extraction. Although different approaches<sup>20,22</sup> have been proposed to make  $\mu_{\rm FE}$  less dependent on various factors, such as  $R_{\rm c}$  and  $L_{\rm ch}$ , none of them is sufficiently

general enough to be widely adopted. Conductivity mobility ( $\mu_{\rm con}$ ) has the advantage of strictly reflecting the channel material properties and the quality of the channel–dielectric interface<sup>22,26</sup>. In a FET,  $\mu_{\rm con}$  (ref. <sup>22</sup>) can be estimated from the sheet resistance of the semiconductor channel and the carrier density,  $n_{\rm S}$  (Table 1); thus, it does not involve the contact resistance or the device structure. High mobility is often a goal for research FETs; when such reports are made, it is critical to clearly state how the values are determined, and ideally multiple approaches (such as  $\mu_{\rm FE}$  and four-probe measurements<sup>21</sup>) are taken to cross-validate the claims. It is worth noting that the usefulness of channel mobility as an indicator of performance in aggressively scaled FETs is debatable, as devices with channel lengths <30 nm are going to be strongly limited by contact resistance (including carrier injection efficiency), with minimal dependence on transport in the channel<sup>27,28</sup>.

The most representative FET parameters are listed in Table 1 as a suggested reporting checklist. Additional parameters are briefly discussed in Supplementary Note 4.

Beyond the parameters in Table 1, showing statistics and variation is strongly encouraged to obtain comprehensive coverage of the device performance. The variation can be shown as error bars, box plots, coefficient of variation or cumulative distribution function (see Supplementary Note 5 for a demonstration). Due to the many non-idealities associated with emerging materials or unconventional device geometries, it is almost unavoidable that there could be considerable uncertainties in many extracted parameters, including  $R_{c}$ ,  $n_{s}$  and mobilities. These parameters are often interdependent. Reducing device variation is a major research theme for the eventual application of emergent FETs. Whatever measurements and specific analysis approaches are taken to determine these

**Table 2** | Suggested benchmarking plots for evaluating device performance compared with other FETs

| Parameter                 | Benchmarking<br>plot                   | Notes                                                                                                                                                                                                                                                              |

|---------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $I_{\min}$ and $I_{\max}$ | $I_{\min}$ versus $I_{\max}$           | <ul> <li>Specify L<sub>ch</sub> or L<sub>ch</sub>/EOT</li> <li>Ideally specify the carrier density at which I<sub>max</sub> is extracted (Supplementary Note 1)</li> </ul>                                                                                         |

| l <sub>sat</sub>          | $I_{\rm sat}$ versus $n_{\rm S}$       | Label $L_{\rm ch}$ and $t_{\rm ch}$ to imply channel resistance                                                                                                                                                                                                    |

| $I_{D}$                   | $I_{\rm D}$ versus $L_{\rm ch}$        | At certain $V_{DS}$ and $n_s$ (for example,<br>$V_{DS} = 1 \text{ V}$ and $n_s = 10^{13} \text{ cm}^{-2}$ )                                                                                                                                                        |

| R <sub>c</sub>            | $R_{\rm c}$ versus $n_{\rm S}$         | <ul> <li>Or benchmark R<sub>c</sub> versus t<sub>ch</sub> at certain n<sub>S</sub></li> <li>Specify if semiconductor in contact regions is gated or not</li> </ul>                                                                                                 |

| $\mu_{con}$               | $\mu_{con}$ versus $t_{ch}$            | For the same material, a thicker channel could have higher mobility due to less surface scattering                                                                                                                                                                 |

| $g_{m}$                   | $g_{ m m}$ versus $n_{ m s}/L_{ m ch}$ | • Because $g_{\rm m} = \frac{W}{L} \mu C_{\rm ins} V_{\rm ov}$ , $g_{\rm m} \propto C_{\rm ins} V_{\rm ov} / L_{\rm ch}$<br>• $n_{\rm S} \approx C_{\rm ins} V_{\rm ov} / q$ near the source end, so $g_{\rm m} \propto n_{\rm S} / L_{\rm ch}$                    |

| SS                        | SS versus C <sub>ins</sub>             | <ul> <li>Larger C<sub>ins</sub> can yield smaller SS</li> <li>Identify Schottky barrier branch and thermal branch</li> <li>Or plot SS versus L<sub>ch</sub> to show short-channel robustness</li> <li>Or plot SS versus log<sub>10</sub>(I<sub>D</sub>)</li> </ul> |

parameters, the details should be clearly and explicitly reported, and our recommended approaches are demonstrated herein.

Once an emerging FET has been systematically parameterized, benchmarking tables and plots are extremely useful for comparing devices from different reports. Because the electric fields are the driving forces within FETs, benchmarking performance metrics based on electric fields is natural. However, special care is needed in considering electric fields in devices, because they are spatially non-uniform and depend on many other factors, such as fringing fields and quantum capacitance  $C_q$ . Thus, the electric fields in nanoscale FETs are more complicated than the simple definition of an applied voltage divided by a physically defined length. For example, it is a reasonable assumption that the channel electric field  $(E_{ch})$ increases linearly from source to drain in the linear region of operation, but  $E_{ch}$  peaks sharply at the drain end of the channel in classical pinch-off (saturation)<sup>29</sup>. To account for this, the average  $E_{ch}$  can be approximated as  $(V_{DS} - 2I_{lin}R_c)/L_{ch}$  in the linear regime, accounting for voltage dropped at the contacts.

The vertical electric field at the source end,  $E_{\rm gate}$ , can be estimated as  $V_{\rm OV}/t_{\rm ins}$  if a planar gate is used. In turn,  $E_{\rm gate}$  and the gate insulator permittivity determine the carrier density in the channel. However, both  $E_{\rm gate}$  and the gate insulator permittivity are rather challenging to measure accurately. One more word of caution is justified: because many low-dimensional materials exhibit a low density of states,  $C_{\rm ins}$  needs to be replaced by  $C_{\rm ins}C_{\rm q}/(C_{\rm ins}+C_{\rm q})$ , where quantum capacitance ( $C_{\rm q}$ ) can be approximated as  $q^2{\rm DOS}$  (density of states) $^{30,31}$ . Only for  $C_{\rm ins}\ll C_{\rm q}$  does this expression become equivalent to  $C_{\rm ins}$ . Because multiple parameters in Table 1 depend on  $n_{\rm S}$ , benchmarking these versus  $n_{\rm S}$  is recommended to evaluate devices from different studies. A suggested list of benchmarking plots to evaluate device parameters and performance metrics is provided in Table 2.

Drain current is the key output of a FET and is also frequently benchmarked and compared. However, many comparisons are oversimplified and not fairly conducted as the drain current depends on many parameters. As mentioned in Table 2, we recommend benchmarking  $I_{\rm D}$  versus  $L_{\rm ch}$  at certain  $V_{\rm DS}$  and  $n_{\rm S}$  values, enabling fair comparison between devices having different channel lengths. On the other hand, if a record  $I_{\rm sat}$  is claimed, we recommend benchmarking the maximum  $I_{\rm sat}$  versus  $n_{\rm S}$ , because it is a much closer indicator for the eventual drive current and ultimately sets the operating delay of a circuit stage (delay  $\tau \propto CV_{\rm DD}/I_{\rm sat}$ ). As mentioned previously, assuming limited short-channel effects,  $I_{\rm sat}$  mainly depends on  $n_{\rm S}$  and not on  $E_{\rm ch}$ . Usually, one performance metric depends on multiple parameters; hence, key parameters should be annotated on the benchmarking plot (Table 2).

## Reporting and benchmarking example

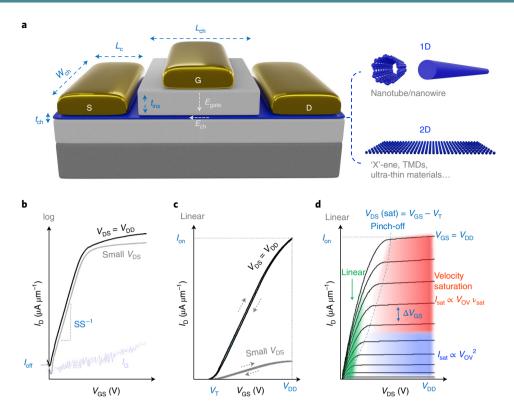

To demonstrate reporting and benchmarking based on the principles proposed above,  $MoS_2$  is chosen as the example emerging channel material because it is among the most studied semiconducting nanomaterials in recent years and represents a family of 2D materials that holds promise for future transistor applications. Figure 2a shows an example transistor based on monolayer (1 L)  $MoS_2$  grown by chemical vapour deposition. The device is top-contacted and back-gated, which is the most common and convenient FET structure used to explore emergent channel materials. The approach is as follows:

Step 1. The structural parameters of the device are determined and labelled (Fig. 2a). In this example, the gate insulator is AlO  $_{\rm s}$ , which is grown by atomic layer deposition with the oxide capacitance ( $C_{\rm ins} \approx 280\,{\rm nF\,cm^{-2}}$ ) evaluated from a capacitance–voltage measurement of a large-area test capacitor. The thickness of the oxide ( $t_{\rm ins} \approx 20\,{\rm nm}$ ) is further confirmed by cross-sectional transmission electron microscope (TEM) imaging. From the thickness and capacitance, the dielectric constant of the oxide is estimated to be  $\varepsilon_{\rm ins} \approx 6$ . Other dimensions, such as  $L_{\rm ch}$ ,  $W_{\rm ch}$  and  $L_{\rm c}$ , are confirmed by scanning electron microscopy (SEM) after electrical characterization.

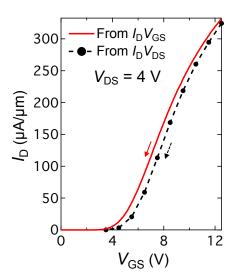

Step 2.  $I_D$ – $V_{GS}$  and  $I_D$ – $V_{DS}$  characterizations are performed, making sure that  $V_{\mathrm{DS}}$  and  $V_{\mathrm{GS}}$  are swept high enough for the device to reach saturation, and the  $V_{\rm GS}$  sweep range is sufficient to observe  $I_{\min}$  in both the linear (low  $V_{DS}$ ) and saturation (high  $V_{DS}$ ) operation regions. An  $I_{\rm max}/I_{\rm min}$  value of ~4×10<sup>7</sup> at  $V_{\rm DS}$  = 4 V can be extracted from the subthreshold curve in Fig. 2b.  $I_{\text{max}}$  is extracted at  $n_{\rm S} \approx 1.4 \times 10^{13} \, {\rm cm}^{-2}$ .  $I_{\rm min}$  is extracted under subthreshold conditions, where  $V_{GS} < V_{T}$ , yielding a negative  $V_{OV}$  and  $n_S \cong 0$ . The larger hysteresis for  $V_{DS} = 4 \text{ V}$  in Fig. 2b,c highlights the impact of the larger source-drain field on the interface charges in the channel. Due to hot-carrier stress from the high  $V_{DS}$  (explained later),  $V_{T}$ increases for high  $V_{\rm DS}$ , resulting in an extracted DIBL of -274 to -436 mV V<sup>-1</sup>, considering the effect of hysteresis. Also, from the transfer curves in Fig. 2c, the maximum  $g_m(sat)$  and  $g_m(lin)$  are estimated to be ~59 μS μm<sup>-1</sup> and ~1.7 μS μm<sup>-1</sup>, respectively. In Fig. 2d, approximate current saturation is observed, with  $I_{\text{sat}}$  around 325  $\mu$ A  $\mu$ m<sup>-1</sup> obtained at  $n_s \approx 1.3 \times 10^{13}$  cm<sup>-2</sup> at  $V_{DS} = 4$  V. The blue and red points show the linear and saturation regions, approximately. The  $I_D$ - $V_{DS}$  spacing is sublinear at the highest  $V_{GS}$ , which is a sign of possible self-heating.

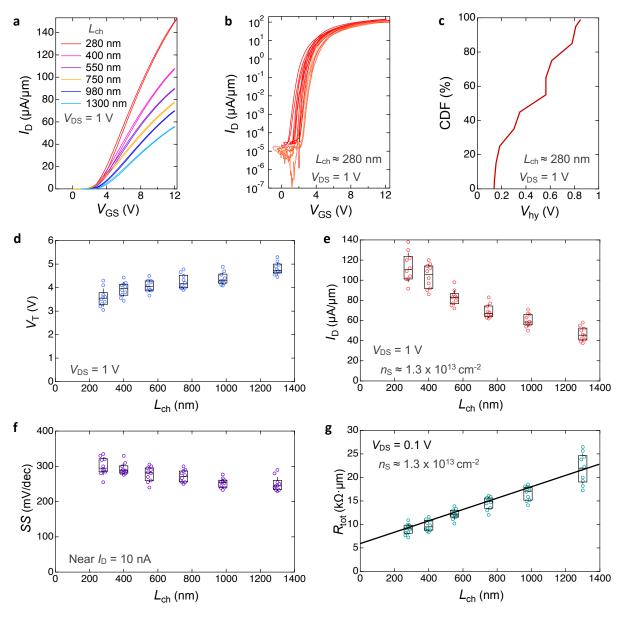

Figure 2a–d is used for primary characterization of one device, and more derived plots are shown in Fig. 2e–h, providing a more complete picture of the device characteristics. The device spread and parameter variations based on ten similar TLM structures are shown in Supplementary Fig. 5. The full range of SS versus  $I_{\rm D}$  is plotted in Fig. 2d, with a minimum SS of 280 mV dec<sup>-1</sup> extracted in the subthreshold regime. Additionally, because  $V_{\rm T}$  depends on  $V_{\rm DS}$ , it is key to extract  $V_{\rm T}$  at the associated  $V_{\rm DS}$  (as noted in Table 1).  $R_{\rm c}$ ,  $R_{\rm sh}$  and subsequently  $\mu_{\rm con}$  are extracted by using a TLM

PERSPECTIVE NATURE ELECTRONICS

**Fig. 2 | Example of reporting device performance for monolayer Au-contacted MoS**<sub>2</sub> **FETs. a**, Device schematic and the basic structural parameters of the MoS<sub>2</sub> FET, a SEM image of a TLM structure with false-coloured MoS<sub>2</sub> area (scale bar, 1 $\mu$ m) and a cross-sectional TEM image of the AlO<sub>x</sub> (scale bar, 20 nm). **b**, Subthreshold ( $I_D$ - $V_{GS}$ ) curve of the device, with  $I_{max}$  and  $I_{min}$  labelled.  $I_G$  is the gate leakage current at  $V_{DS}$  = 4 V. The curve for  $V_{DS}$  = 1V is intentionally not shown so the plot is less crowded. **c**, Transfer ( $I_D$ - $V_{GS}$ ) curves of the device, showing larger hysteresis with larger  $V_{DS}$ . **d**, Output ( $I_D$ - $V_{DS}$ ) curves of the device.  $V_{GS}$  changes in steps of 1V. **e**, SS versus  $I_D$  for both forwards and backwards  $V_{GS}$  sweeps in **b**. **f**, Extraction of  $R_c$  from the TLM structure in **a**.  $R_{tot}$  is extracted at  $V_{DS}$  = 100 mV. **g**, Contact resistance versus  $n_S$ , showing the contact gating effect that is a result of the device operating as a Schottky barrier transistor with the gate modulating the semiconductor in the source-drain contact regions<sup>32</sup>. **h**, Extracted sheet resistance (left axis) and conductivity mobility (right axis) versus  $n_S$ . In **g** and **h**, error bars reflect the 90% confidence interval from a least-squares fit of the TLM.

structure as shown in Fig. 2f–h. The  $R_{\rm c}$  is estimated to be ~2.1 k $\Omega$ µm, which is comparable to the  $R_{\rm ch}$  of  $2.8\,{\rm k}\Omega$ µm for the device with channel length of 280 nm. The relation between  $n_{\rm s}$  and extracted  $R_{\rm c}$  is plotted in Fig. 2g to show the effect of the overall back-gate on the contact resistance (that is, contact gating <sup>32–34</sup>). Figure 2h shows that  $\mu_{\rm con}$  decreases from 59 to  $40\,{\rm cm}^2{\rm V}^{-1}\,{\rm s}^{-1}$  with increasing  $n_{\rm s}$ , probably due to the increased electron scattering with the oxide surface roughness.

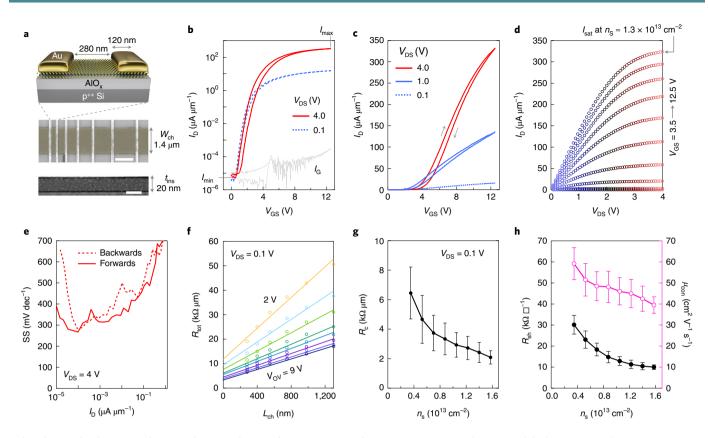

Step 3. As a simplified example, we benchmark key device performance parameters in Fig. 3 (a limited number of reports are included). Currently, most papers do not report  $I_D$ – $V_{GS}$  at  $V_{DS}$  (sat) or close to  $V_{\rm DD}$ , as recommended above. Hence, plotting  $I_{\rm min}$  versus  $I_{\text{max}}$  at certain  $V_{\text{DS}}$  (for example,  $V_{\text{DS}} = 1 \text{ V}$ ) while annotating  $L_{\text{ch}}$  is an acceptable approach (Fig. 3a). The upper limit of the carrier density is set at  $n_s = 10^{13} \,\mathrm{cm}^{-2}$ , ensuring a fair comparison of  $I_{\mathrm{max}}$ . The  $I_{\text{max}}/I_{\text{min}}$  ratio annotated on the right axis is also shown in the dashed lines in Fig. 3a. Owing to better electrostatic control from the gate, devices with a larger  $L_{ch}/EOT$  ratio tend to yield higher  $I_{max}/I_{min}$ (where EOT is the equivalent oxide thickness). Other parameters also play a role, such as the leakage currents through the gate insulator or from source to drain. Large channel width can also produce a more accurate width-normalized  $I_{\min}$ , especially when  $I_{\min}$  is below the instrument noise floor. For example, a relatively high  $I_{

m max}/I_{

m min}$ ratio has been demonstrated in ref. 35 in devices with 20-µm channel width. Further study is still needed to investigate how to achieve high  $I_{\text{max}}$  and small  $I_{\text{min}}$  in aggressively scaled devices (small  $L_{\text{ch}}$ ,  $L_{\text{c}}$ and EOT).

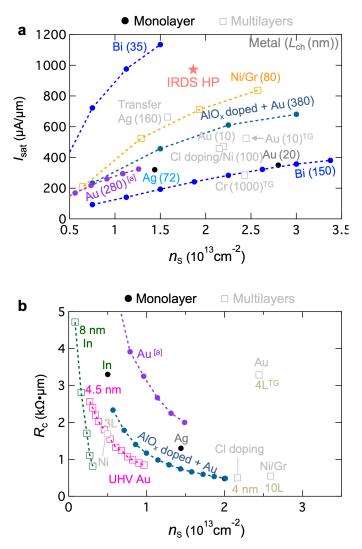

As mentioned previously, a high drain current in the saturation regime is a key performance metric. In Fig. 3b,  $I_{\rm sat}$  is plotted versus  $n_{\rm S}$  from representative studies of FETs based on MoS<sub>2</sub> as the channel material. We note that  $I_{\rm sat}$  is extracted at different  $V_{\rm DS}$  values, because different devices have different channel lengths, as annotated in Fig. 3b. We caution against plotting  $I_{\rm sat}/I_{\rm ch}$  versus  $n_{\rm S}$ , because it implies that  $L_{\rm ch}$  is the main limiting factor for  $I_{\rm sat}$ , which is not necessarily true, especially for scaled devices where contact resistance typically dominates  $I_{\rm sat}$  performance. Importantly, it is clear that  $I_{\rm sat}$  needs to be further improved to meet the high-performance target of the most recent technology guidelines (at  $V_{\rm DD} \approx 0.65$  V near 2030)<sup>36</sup>. Many reports have already used high  $n_{\rm S}$  but fell short regarding  $I_{\rm sat}$  even with channel lengths down to ~10 nm (ref. <sup>37</sup>), being strongly limited by their contacts.

Recently, semimetal contacts such as bismuth have been shown to produce high-quality contacts  $^{38}$ . It is nevertheless noteworthy that the two Bi-1L MoS $_2$  devices have a wide range of  $I_{\rm sat}$  performance, encompassing all the other devices in Fig. 3b, yet the channel length difference between the two devices is only 115 nm. Interestingly, one of the Bi-contacted devices ( $L_{\rm ch}$ =150 nm) actually underperforms other Au-contacted devices with longer channel lengths. Hence, although some approaches show potential to achieve the International Roadmap for Devices and Systems (IRDS) high-performance goal of  $I_{\rm sat}$  for the post-2030 era  $^{36}$ , further investigation is still needed to reliably and reproducibly realize high  $I_{\rm sat}$  from a monolayer channel. In next-generation FETs,  $I_{\rm sat}$  could also be increased by shifting to nanosheet device designs, which stack

**Fig. 3 | Example benchmarking device performance of monolayer MoS<sub>2</sub> FETs. a**, Benchmarking  $I_{min}$  versus  $I_{max}$ . The  $I_{max}$  is extracted at  $n_s = 10^{13}$  cm<sup>-2</sup>. For simplicity,  $I_{min}$  values of the data points are extracted at their respective smallest current. More rigorous benchmarking of  $I_{min}$  versus  $I_{max}$  is described in Supplementary Note 1. **b**, Benchmarking  $I_{sat}$  versus  $n_s$ , where the channel length (in nm) is labelled next to the contact metals used in the devices.  $I_{sat}$  values are extracted at different  $V_{DS}$  (listed in Supplementary Table 1). These devices do not have the same  $V_{DS}$ (sat) as devices with different channel lengths and saturate at different  $V_{DS}$ . The IRDS high performance (HP) is shown in a range of  $n_S$  to represent uncertainties of the carrier density in future generation technologies. **c**, Benchmarking  $I_D$  versus  $I_{CD}$  and  $I_D$  versus  $I_D$  versus  $I_D$  and  $I_D$  versus  $I_$

multiple channels vertically to improve current density in the same device footprint<sup>39</sup>.

In some reports, a proper saturation current is not given. Also, because different devices use different channel lengths,  $I_{\rm sat}$  is often extracted at different  $V_{\rm DS}$ . To highlight the impact of channel length, we recommend benchmarking  $I_{\rm D}$  versus  $L_{\rm ch}$  at  $V_{\rm DS}=1\,\rm V$  and  $n_{\rm S}=10^{13}\,\rm cm^{-2}$ . This plot enables a direct comparison of devices with similar  $L_{\rm ch}$ . In Fig. 3c, with channel length decreasing from 200 nm to 38 nm, devices contacted by both Bi³8 and Sn⁴0 yield relatively large increases in drain current. We note that the Bi-contacted devices are based on different MoS₂ films. The different quality of the MoS₂ may partially contribute to the large increase of  $I_{\rm D}$  with a relatively small change in  $L_{\rm ch}$ . Nevertheless, Fig. 3c,d presents the potential of atomically thin materials for producing high drain current, especially for scaled devices.

In Fig. 3d,  $R_c$  is plotted against  $n_s$  considering most devices have gated contacts (that is, the back-gate modulates the channel and

contacts<sup>32-34</sup>). Although some reported R<sub>c</sub> values reach below  $500 \Omega \mu m$ , their TLM extractions are all based on channel resistance-dominated devices, which can lead to questionable validity in their claimed  $R_c$  (an artificially small or even a negative  $R_c$  can be extracted, see Supplementary Note 3 for details). We advocate that, if a record  $R_c$  is claimed from TLM,  $R_{sh}$  should be cross-examined by using other methods such as four-probe measurements, which can provide a relatively accurate estimation of  $R_{\rm sh}$  versus  $n_{\rm S}$ (Supplementary Note 3). With  $R_{\rm sh}$  versus  $n_{\rm S}$  from four-probe measurements,  $R_c$  versus  $n_s$  can be derived by deducting the  $R_{ch} = R_{sh}L_{ch}$ from  $R_{tot}$  to confirm the TLM extracted value. Showing extraction of R<sub>c</sub> from many TLM structures can also increase confidence in the data by providing an average value of the  $R_c$  rather than just the minimal value from a single TLM<sup>41,42</sup>. Furthermore,  $R_c$  is heavily impacted by contact gating, as is evident from the similar trends of  $R_c$  versus  $n_s$  observed in different studies. Accordingly, further research is needed to obtain a small  $R_c$  without gating the contacts.

PERSPECTIVE NATURE ELECTRONICS

Looking forward, many opportunities remain to develop transistors that simultaneously have small contact resistance, high  $I_{\rm sat}$  large  $I_{\rm max}/I_{\rm min}$  ratio and minimal short-channel effects by using emergent nanomaterials. To achieve this technological goal, interface engineering at the contacts and gate dielectric needs to be further investigated 43–45, along with progress in material synthesis 46 and integration 47. Moreover, it is important to focus on channel thicknesses below ~3 nm, where low-dimensional nanomaterials can excel compared to Si, which suffers from poor carrier transport properties and a widened bandgap in this thickness regime 48.

In addition to the example benchmarking plots in Fig. 3, other benchmarks can also be used to compare different devices, for example, as included in Table 2, plotting  $I_{\rm max}/I_{\rm min}$  versus  $t_{\rm ch}$  or  $I_{\rm max}/I_{\rm min}$  versus  $L_{\rm ch}/{\rm EOT}$  to compare the off-state device performance. Plotting SS versus  $C_{\rm ins}$  or SS versus  $\log_{10}(I_{\rm D})$  (ref. <sup>49</sup>) can be used to evaluate subthreshold behaviour and trends across different devices. Finally, to show the quality of the channel materials, the channel sheet resistance or conductivity mobility can be plotted versus carrier densities, as in Fig. 2h. Representative reports with relatively large  $I_{\text{sat}}$  are listed in Supplementary Table 1, including results for FETs with both monolayer and multilayer MoS2 channels (example benchmarking plots are provided in Supplementary Note 6). In the literature, notable benchmarking examples can be found in refs. 38,50, which highlight different channel materials, and in ref. 51, which focuses on device performance in integrated circuits (speed, gain, density, power consumption, fan-out capabilities, and so on).

#### Conclusions

Our guidelines should help put key performance metrics in a proper context and enable researchers to effectively report and benchmark emergent transistors based on various emergent nanomaterials. Although each of the listed metrics is important, it is not necessary—nor always possible—to extract and present all of them. As such, it is essential to completely describe the device geometry, to collect and report appropriate current-voltage characteristics, and to describe in detail the procedures followed in the experiments. The approaches used to analyse data and extract benchmarking metrics should also be described in detail. Depending on the context and need, we recommend three sets of parameters to report and benchmark. The first includes maximum saturation current, on/off current ratio, transconductance and subthreshold swing. These values can be directly obtained from the measured I-V characteristics that cover both linear and saturation regimes. These values are mainly determined by the intrinsic material properties, gate stack configuration and contact quality. The second includes the derived parameters such as mobilities and contact resistance, where uncertainty and statistical spread on these derived parameters should be shown. The third set of parameters are those specific to certain transistor demonstrations based on the target application<sup>52,53</sup>. For example, DIBL is essential when reporting and evaluating ultra-scaled FETs. It is important—whenever possible—to benchmark against other novel materials and also the state of the art in mature technology<sup>38,50</sup>. By using these guidelines, it should be possible to comprehensively and consistently reveal, highlight, discuss, compare and evaluate device performance, thus helping to identify advances and opportunities in the search for improved transistors.

## Data availability

The data used in this paper are available from the corresponding authors upon reasonable request.

Received: 4 November 2021; Accepted: 16 June 2022; Published online: 29 July 2022

#### References

- Chen, Z. et al. An integrated logic circuit assembled on a single carbon nanotube. Science 311, 1735 (2006).

- Franklin, A. D. et al. Sub-10-nm carbon nanotube transistor. Nano Lett. 12, 758–762 (2012).

- 3. Geim, A. K. Graphene: status and prospects. Science 324, 1530-1534 (2009).

- Ye, P. D. et al. Phosphorene an unexplored 2D semiconductor with a high hole mobility. ACS Nano 8, 4033–4041 (2014).

- Tao, L. et al. Silicene field-effect transistors operating at room temperature. Nat. Nanotechnol. 10, 227–231 (2015).

- Wang, Y. et al. Field-effect transistors made from solution-grown two-dimensional tellurene. Nat. Electron. 1, 228–236 (2018).

- Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS, transistors. Nat. Nanotechnol. 6, 147–150 (2011).

- Das, S., Chen, H. Y., Penumatcha, A. V. & Appenzeller, J. High performance multilayer MoS<sub>2</sub> transistors with scandium contacts. *Nano Lett.* 13, 100–105 (2013).

- English, C. D., Shine, G., Dorgan, V. E., Saraswat, K. C. & Pop, E. Improved contacts to MoS<sub>2</sub> transistors by ultra-high vacuum metal deposition. Nano Lett. 16, 3824–3830 (2016).

- Sirringhaus, H. 25th anniversary article: organic field-effect transistors: the path beyond amorphous silicon. Adv. Mater. 26, 1319–1335 (2014).

- Waldrip, M., Jurchescu, O. D., Gundlach, D. J. & Bittle, E. G. Contact resistance in organic field-effect transistors: conquering the barrier. Adv. Funct. Mater. 30, 1904576 (2020).

- Li, S. et al. Nanometre-thin indium tin oxide for advanced high-performance electronics. Nat. Mater. 18, 1091–1097 (2019).

- Li, M. Y., Su, S. K., Wong, H. S. P. & Li, L. J. How 2D semiconductors could extend Moore's law. *Nature* 567, 169–170 (2019).

- Datye, I. M. et al. Reduction of hysteresis in MoS<sub>2</sub> transistors using pulsed voltage measurements. 2D Mater. 6, 011004 (2019).

- Streetman, B. G. & Banerjee, S. K. Solid State Electronic Devices 6th edn (Pearson, 2006).

- Smithe, K. K. H., English, C. D., Suryavanshi, S. V. & Pop, E. High-field transport and velocity saturation in synthetic monolayer MoS<sub>2</sub>. Nano Lett. 18, 4516–4522 (2018).

- Pinckney, N. et al. Impact of FinFET on near-threshold voltage scalability. IEEE Des. Test 34, 31–38 (2017).

- Ortiz-Conde, A. et al. A review of recent MOSFET threshold voltage extraction methods. Microelectron. Reliab. 42, 583–596 (2002).

- Ghibaudo, G. New method for the extraction of MOSFET parameters. Electron. Lett. 24, 543–545 (1988).

- 20. Chang, H. Y., Zhu, W. & Akinwande, D. On the mobility and contact resistance evaluation for transistors based on MoS<sub>2</sub> or two-dimensional semiconducting atomic crystals. *Appl. Phys. Lett.* **104**, 113504 (2014).

- Pang, C. et al. Mobility extraction in 2D transition metal dichalcogenide devices—avoiding contact resistance implicated overestimation. Small 17, 2100940 (2021).

- Schroder, D. K. Semiconductor Material and Device Characterization 3rd edn (Wiley, 2015).

- Mleczko, M. J. et al. HfSe<sub>2</sub> and ZrSe<sub>2</sub>: two-dimensional semiconductors with native high-k oxides. Sci. Adv. 3, e1700481 (2017).

- Nasr, J. R., Schulman, D. S., Sebastian, A., Horn, M. W. & Das, S. Mobility deception in nanoscale transistors: an untold contact story. *Adv. Mater.* 31, 1806020 (2019).

- Bittle, E. G., Basham, J. I., Jackson, T. N., Jurchescu, O. D. & Gundlach, D. J. Mobility overestimation due to gated contacts in organic field-effect transistors. *Nat. Commun.* 7, 10908 (2016).

- Smithe, K. K. H., English, C. D., Suryavanshi, S. V. & Pop, E. Intrinsic electrical transport and performance projections of synthetic monolayer MoS<sub>2</sub> devices. 2D Mater. 4, 011009 (2017).

- Franklin, A. D. Nanomaterials in transistors: from high-performance to thin-film applications. Science 349, aab2750 (2015).

- Das, S. et al. Transistors based on two-dimensional materials for future integrated circuits. Nat. Electron. 4, 786–799 (2021).

- Pao, H. C. & Sah, C. T. Effects of diffusion current on characteristics of metal-oxide (insulator)-semiconductor transistors. Solid State Electron. 9, 927–937 (1966).

- John, D. L., Castro, L. C. & Pulfrey, D. L. Quantum capacitance in nanoscale device modeling. J. Appl. Phys. 96, 5180 (2004).

- Xu, H., Zhang, Z. & Peng, L.-M. Measurements and microscopic model of quantum capacitance in graphene. *Appl. Phys. Lett.* 98, 133122 (2011).

- Appenzeller, J., Zhang, F., Das, S. & Knoch, J. in 2D Materials for Nanoelectronics (eds Houssa, M. et al.) 207–240 (CRC Press, 2016).

- Arutchelvan, G. et al. From the metal to the channel: a study of carrier injection through the metal/2D MoS<sub>2</sub> interface. *Nanoscale* 9, 10869–10879 (2017).

- Prakash, A., Ilatikhameneh, H., Wu, P. & Appenzeller, J. Understanding contact gating in Schottky barrier transistors from 2D channels. Sci. Rep. 7, 12596 (2017).

- Illarionov, Y. Y. et al. Improved hysteresis and reliability of MoS<sub>2</sub> transistors with high-quality CVD growth and Al<sub>2</sub>O<sub>3</sub> encapsulation. *IEEE Electron Device* Lett. 38, 1763–1766 (2017).

- 36. IEEE International Roadmap for Devices and Systems (IEEE, 2020); https://irds.ieee.org/

- Patel, K. A., Grady, R. W., Smithe, K. K. H., Pop, E. & Sordan, R. Ultra-scaled MoS<sub>2</sub> transistors and circuits fabricated without nanolithography. 2D Mater. 7, 015018 (2020).

- Shen, P.-C. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. *Nature* 593, 211–217 (2021).

- Ahmed, Z. et al. Introducing 2D-FETs in device scaling roadmap using DTCO. In Proc. 2020 International Electron Devices Meeting, IEDM 22.5.1–22.5.4 (IEEE, 2020); https://doi.org/10.1109/IEDM13553.2020.9371906

- 40. Chou, A. S. et al. High on-state current in chemical vapor deposited monolayer MoS<sub>2</sub> nFETs with Sn ohmic contacts. *IEEE Electron Device Lett.* **42**, 272–275 (2021).

- Sebastian, A., Pendurthi, R., Choudhury, T. H., Redwing, J. M. & Das, S. Benchmarking monolayer MoS<sub>2</sub> and WS<sub>2</sub> field-effect transistors. *Nat. Commun.* 12, 693 (2021).

- Kumar, A., Tang, A., Philip Wong, H. S. & Saraswat, K. Improved contacts to synthetic monolayer MoS<sub>2</sub>—a statistical study. In *Proc. IEEE International Interconnect Technology Conference* 1–3 (IEEE, 2021); https://doi.org/10.1109/ IITC51362.2021.9537515

- Cheng, Z., Price, K. & Franklin, A. D. Contacting and gating 2-D nanomaterials. *IEEE Trans. Electron Devices* 65, 4073–4083 (2018).

- Illarionov, Y. Y. et al. Insulators for 2D nanoelectronics: the gap to bridge. Nat. Commun. 11, 3385 (2020).

- 45. Cheng, Z. et al. Are 2D interfaces really flat? ACS Nano 16, 5316-5324 (2022).

- Zhou, J. et al. A library of atomically thin metal chalcogenides. *Nature* 556, 355–359 (2018).

- Liu, Y. et al. Van der Waals heterostructures and devices. Nat. Rev. Mater. 1, 16042 (2016).

- 48. Uchida, K., Koga, J. & Takagi, S. Experimental study on electron mobility in ultrathin-body silicon-on-insulator metal-oxide-semiconductor field-effect transistors. *J. Appl. Phys.* **102**, 074510 (2007).

- Haratipour, N., Namgung, S., Oh, S. H. & Koester, S. J. Fundamental limits on the subthreshold slope in Schottky source/drain black phosphorus field-effect transistors. ACS Nano 10, 3791–3800 (2016).

- 50. Liu, Y. et al. Promises and prospects of two-dimensional transistors. *Nature* **591**, 43–53 (2021).

- Nikonov, D. E. & Young, I. A. Benchmarking of beyond-CMOS exploratory devices for logic integrated circuits. *IEEE J. Explor. Solid State Comput. Devices Circuits* 1, 3–11 (2015).

- Abuzaid, H., Williams, N. X. & Franklin, A. D. How good are 2D transistors? An application-specific benchmarking study. *Appl. Phys. Lett.* 118, 030501 (2021).

- 53. Lemme, M. C., Akinwande, D., Huyghebaert, C. & Stampfer, C. 2D materials for future heterogeneous electronics. *Nat. Commun.* 13, 1392 (2022).

- McClellan, C. J., Yalon, E., Smithe, K. K. H., Suryavanshi, S. V. & Pop, E. High current density in monolayer MoS<sub>2</sub> doped by AlO<sub>x</sub>. ACS Nano 15, 1587–1596 (2021).

- Lembke, D. & Kis, A. Breakdown of high-performance monolayer MoS<sub>2</sub> transistors. ACS Nano 6, 10070–10075 (2012).

- Kumar, A. et al. Sub-200 Ωµm alloyed contacts to synthetic monolayer MoS<sub>2</sub>. In Proc. IEEE International Electron Devices Meeting (IEDM) 154–157 (IEEE, 2021).

- Chou, A. et al. Antimony semimetal contact with enhanced thermal stability for high performance 2D electronics. In *Proc. IEEE International Electron Devices Meeting (IEDM)* 150–153 (IEEE, 2021).

- Wang, Y. et al. Van der Waals contacts between three-dimensional metals and two-dimensional semiconductors. *Nature* 568, 70–74 (2019).

## Acknowledgements

We acknowledge H. Zhang and A. Davydov from the National Institute of Standards and Technology for their help with the TEM images of the oxide in Fig. 2. We acknowledge G. Li and L. Cao from North Carolina State University for providing the chemical-vapour-deposited MoS<sub>2</sub> film. This work is supported by NEWLIMITS, a centre in nCORE, a Semiconductor Research Corporation (SRC) programme sponsored by NIST through award no. 70NANB17H041. A.D.F. acknowledges support from the National Science Foundation under grant no. ECCS 1915814. M.C.L. acknowledges funding from the European Union's Horizon 2020 research and innovation programme under grant agreements nos. 881603 (Graphene Flagship), 952792 (2D-EPL) and 829035 (QUEFORMAL), as well as the Deutsche Forschungsgemeinschaft (DFG, German Research Foundation) through grants nos. LE 2440/7-1 and LE 2440/8-1. Furthermore, support by the Bundesministerium für Bildung und Forschung (BMBF, German Ministry of Education and Research) through grants nos. 03XP0210 (GIMMIK) and 03ZU1106 (NeuroSys) is acknowledged. L.-M.P. acknowledges the National Science Foundation of China under grant no. 61888102. S.J.K. acknowledges support from the NSF through award no. DMR-1921629. Fabrication and measurements were partially performed at the NIST Center for Nanoscale Science and Technology and at Duke Shared Manufacturing and Instrument Facility (SMIF). Certain commercial equipment, instruments, or materials are identified in this paper to specify the experimental procedure adequately. Such identifications are not intended to imply recommendation or endorsement by the National Institute of Standards and Technology (NIST), nor is it intended to imply that the materials or equipment identified are necessarily the best available for the purpose.

#### **Author contributions**

All authors contributed to the preparation of the manuscript.

## Competing interests

The authors declare no competing interests.

### Additional information

**Supplementary information** The online version contains supplementary material available at https://doi.org/10.1038/s41928-022-00798-8.

Correspondence should be addressed to Zhihui Cheng, Aaron D. Franklin or Curt A. Richter.

**Peer review information** *Nature Electronics* thanks Han Wang and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Reprints and permissions information is available at www.nature.com/reprints.

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

© Springer Nature Limited 2022, corrected publication 2022

## **Supplementary information**

# How to report and benchmark emerging field-effect transistors

In the format provided by the authors and unedited

## Supplementary Information for

## How to Report and Benchmark Emerging Field-Effect Transistors

Zhihui Cheng<sup>1,2,†</sup>, Chin-Sheng Pang<sup>2</sup>, Peiqi Wang<sup>3</sup>, Son T. Le<sup>1,4</sup>, Yanqing Wu<sup>5</sup>, Davood Shahrjerdi<sup>6,7</sup>, Iuliana Radu<sup>8</sup>, Max C. Lemme<sup>9,10</sup>, Lian-Mao Peng<sup>11</sup>, Xiangfeng Duan<sup>3</sup>, Zhihong Chen<sup>2</sup>, Joerg Appenzeller<sup>2</sup>, Steven J. Koester<sup>12</sup>, Eric Pop<sup>13</sup>, Aaron D. Franklin<sup>14,15,†</sup>, Curt A. Richter<sup>1,†</sup>

<sup>1</sup>Nanoscale Device Characterization Division, National Institute of Standards and Technology, Gaithersburg, MD 20899, USA. <sup>2</sup>Department of Electrical and Computer Engineering, Purdue University, West Lafayette, IN 47907, USA. <sup>3</sup>Department of Chemistry and Biochemistry, University of California, Los Angeles, Los Angeles, CA 90095, USA. <sup>4</sup>Theiss Research, La Jolla, CA 92037, USA. <sup>5</sup>School of Integrated Circuits, Peking University, Beijing 100871, China. <sup>6</sup>Electrical and Computer Engineering, New York University, Brooklyn, NY 11201, USA. <sup>7</sup>Center for Quantum Phenomena, Physics Department, New York University, New York, NY 10003, USA. <sup>8</sup>IMEC, Leuven, Belgium. <sup>9</sup>RWTH Aachen University, Chair of Electronic Devices, Otto-Blumenthal-Str. 2, Aachen 52074, Germany. <sup>10</sup>AMO GmbH, Advanced Microelectronic Center Aachen, Otto-Blumenthal-Str. 25, Aachen, 52074 Germany. <sup>11</sup>Key Laboratory for the Physics and Chemistry of Nanodevices and Center for Carbon-based Electronics, Department of Electronics, Peking University, Beijing, China. <sup>12</sup>Department of Electrical and Computer Engineering, University of Minnesota, Minneapolis, MN 55455 USA. <sup>13</sup>Department of Electrical and Computer Engineering, Stanford University, Stanford, CA 94305, USA. <sup>14</sup>Department of Chemistry, Duke University, Durham, NC 27708, USA. <sup>†</sup>: corresponding authors.

**Note S1**: Rigorously reporting and benchmarking  $I_{\text{max}}/I_{\text{min}}$

Note S2: Different methods to extract threshold voltage  $V_T$  and its uncertainties

**Note S3**: Extracting  $R_c$  from TLM

Note S4: Additional Parameters

**Note S5**: Demonstration of device spread and parameter variations

Note S6: Benchmarking devices with different channel thicknesses

## Note S1: Rigorously reporting and benchmarking $I_{\text{max}}/I_{\text{min}}$

The  $I_{\rm max}/I_{\rm min}$  ratio is the most-used figure of merit for evaluating off-state performance of a transistor and it depends on multiple factors. First,  $I_{\rm max}/I_{\rm min}$  is impacted by material properties such as material quality, bandgaps, and doping conditions. Secondly, the specific device structure and geometry, including the channel length and gate capacitance, also affect the achievable  $I_{\rm max}/I_{\rm min}$ . Thirdly, the same device operating at different operation regimes might also have different  $I_{\rm max}/I_{\rm min}$ . Combined with the absence of a well-defined  $V_{\rm DD}$ , these factors make rigorous reporting and benchmarking guidelines strongly desired for  $I_{\rm max}/I_{\rm min}$ . Rigorously reporting  $I_{\rm max}/I_{\rm min}$  involves clearly identifying the  $V_{\rm DS}$  and  $V_{\rm GS}$  values at which the  $I_{\rm max}$  and  $I_{\rm min}$  are extracted. This practice will help fairly benchmark  $I_{\rm max}/I_{\rm min}$  between different devices.

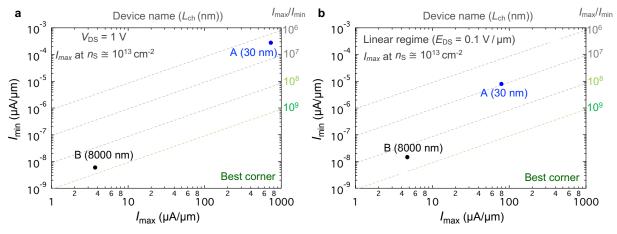

Similar to Fig. 3a, Fig. S1a represents benchmarking  $I_{\text{max}}/I_{\text{min}}$  at  $V_{\text{DS}}=1$  V, which is a commonly used bias condition when obtaining subthreshold curves. Under  $V_{\text{DS}}=1$  V, short-channel devices (e.g., Device A) may operate at the saturation regime, whereas long-channel devices (e.g., Device B) at the linear regime. While using the same  $V_{\text{DS}}=1$  V is a convenient and simple method, the  $I_{\text{max}}/I_{\text{min}}$  likely represent different operation regimes for the two example devices. For a more precise comparison, instead of extracting the  $I_{\text{max}}$  and  $I_{\text{min}}$  at the same  $V_{\text{DS}}$  value for the different devices, it is possible to ensure they are extracted in the same regime (linear or saturation) by using the drain-source electric field instead of  $V_{\text{DS}}$ ; e.g.,  $E_{\text{DS}}=0.1$  V/ $\mu$ m for the linear regime. This improved comparison is demonstrated in Fig. S1b, where the carrier density at which the  $I_{\text{max}}$  is extracted is also labeled, ensuring that different devices have the same carrier density in their  $I_{\text{max}}$  extraction.

**Fig. S1** | Rigorously benchmarking  $I_{\text{max}}/I_{\text{min}}$ . **a**, Benchmarking  $I_{\text{max}}/I_{\text{min}}$  at  $V_{\text{DS}} = 1$  V, similar to Fig. 3a. Devices A and B are not actual experimental data and are used to demonstrate benchmarking devices with different channel lengths. The carrier density at which the  $I_{\text{max}}$  is extracted is also labeled. **b**, Benchmarking  $I_{\text{max}}/I_{\text{min}}$  at the same operation regime, which is the linear regime with drain-to-source field  $E_{\text{DS}} = 0.1$  V/μm used as an example. Note, the diagonal dashed lines indicate certain values of  $I_{\text{max}}/I_{\text{min}}$ .

Additional factors can impact  $I_{\text{max}}/I_{\text{min}}$  ratio. When benchmarking devices with the same channel material but with different channel thicknesses, plotting  $I_{\text{max}}/I_{\text{min}}$  vs.  $t_{\text{ch}}$  is suggested. It is noteworthy that  $I_{\text{max}}/I_{\text{min}}$  also depends on channel length and the equivalent oxide thickness (EOT) of the gate insulator. When the devices to be benchmarked have the same channel thickness, then benchmarking  $I_{\text{max}}/I_{\text{min}}$  vs.  $L_{\text{ch}}/\text{EOT}$  should be considered. In addition,  $I_{\text{min}}$  can be limited by the measurement instrumentation, especially in materials with larger band gap such as monolayer TMDs. Additional factors impacting  $I_{\text{max}}/I_{\text{min}}$  include contact resistance (which limits  $I_{\text{max}}$ ), leakage currents (which dominate  $I_{\text{min}}$ ) and parasitic capacitances (which affect electrostatic control of the gate), etc.

## Note S2: Different methods to extract threshold voltage $V_T$ and its uncertainties

## Different methods to extract $V_T$

A standard method to extract the  $V_{\rm T}$  is not yet available. Refs. <sup>4–7</sup> have investigated and compared different  $V_{\rm T}$  extraction methods. Specifically, in Ref. <sup>4</sup>, the authors investigated eleven approaches to extract the  $V_{\rm T}$  and found that similar  $V_{\rm T}$  values in the linear regime can be extracted. In Refs. <sup>5,6</sup>, the authors proposed the Y-function method to eliminate the  $R_{\rm c}$  effect when evaluating mobility values. In their studies, the  $V_{\rm T}$  is extracted from the  $I_{\rm D}/g_{\rm m}^{0.5}$  curve.

## Uncertainty of $V_T$ induced by I-V sweeps

The threshold voltage  $V_T$  uncertainties can propagate to the estimation of carrier density. Fig. S2 shows an example of  $V_T$  shift due to different sweeps  $(I_D-V_{GS} \text{ vs. } I_D-V_{DS})$  on the same device illustrated in Fig. 2c.

Fig. S2 | Comparison of transfer curves at  $V_{\rm DS}$  = 4 V from  $I_{\rm D}$ - $V_{\rm GS}$  sweep (red) and extraction from  $I_{\rm D}$ - $V_{\rm DS}$  sweeps (black) based on data in Figures 2b,d of the main text. The direction of the sweeps is the same (backward). A  $V_{\rm T}$  shift of ~0.6 V is observed comparing the  $I_{\rm D}$ - $V_{\rm GS}$  and  $I_{\rm D}$ - $V_{\rm DS}$  sweeps. We presume this shift arises from hot-carrier stress during the  $I_{\rm D}$ - $V_{\rm DS}$  sweeping at high  $V_{\rm DS}$  and  $V_{\rm GS}$ . Due to high electric fields, energetic electrons become trapped in the gate oxide as fixed charges<sup>8</sup>, increasing the  $V_{\rm T}$ . This phenomenon highlights the dependence of  $V_{\rm T}$  on  $I_{\rm D}$ - $V_{\rm DS}$  sweeping.

## Note S3: Extracting $R_c$ from TLM

Extracting  $R_c$  from TLM data can lead to significant uncertainties. As a reminder, TLM data is a plot of the total resistance ( $R_{tot}$ ) from a set of devices having all things consistent with their structure and materials except their channel length. TLM data is plotted as  $R_{tot}$  vs  $L_{ch}$ , where the  $R_{tot} = R_{ch} + 2R_c$  =  $R_{sh}L_{ch} + 2R_c$ , which means when the channel length is zero (y-axis intercept)  $R_{tot} = 2R_c$ . A reliable  $R_c$  must be derived from TLM data that includes devices in the short-channel limit, where  $R_c$  dominates the total resistance or at least is comparable to the  $R_{ch}$ . Ideally, the sheet resistance and its variation need to be sufficiently small; otherwise, a small variation in  $R_{sh}$  could lead to substantial errors in  $R_c$ . Three examples of TLM data are presented in Fig. S3a, all claiming an  $R_c$  of 500  $\Omega$ · $\mu$ m, based on the intercepts to the  $R_{tot}$  axis. However, due to the larger  $R_{sh}$ , the uncertainty of  $R_c$  in TLM A is significantly larger than TLM B (e.g., a small change in  $R_{sh}$  for TLM A would result in a large change in the extracted  $R_c$ ). In TLM A, the shortest channel device has an  $R_{tot}$  of 10 k $\Omega$ · $\mu$ m, which is much larger than the claimed  $R_c$  of 500  $\Omega$ · $\mu$ m, whereas in TLM B, the  $R_{tot}$  is 2 k $\Omega$ · $\mu$ m and the claimed  $R_c$  is 500  $\Omega$ · $\mu$ m. As noted above, with a slight variation in the  $R_{sh}$  in TLM A, the  $R_c$  might be extracted as a very small (and often untrue) value or even a negative value.

Hence, it is critical to have both of the following in a TLM: 1) devices with channel length small enough to ensure  $2R_c$  dominates  $R_{tot}$  and 2) a sufficient number of longer channel length devices to ensure a reliable  $R_{sh}$  extraction based on a linear fit. Another possible scenario to avoid is illustrated with TLM C, which represents a TLM data set where all of the devices are  $2R_c$  dominated thus leading to an inaccurate estimation of  $R_{sh}$ . This comparison further highlights the need for proper TLM data; as a summary, a valid TLM data set should have at least four channels and include at least one each of contact and channel resistance-dominated devices.

**Fig. S3** | **a**, Demonstration of TLM data sets with all  $R_{ch}$ -dominant devices (TLM A, leading to unreliable  $R_c$  extraction), all  $R_c$ -dominant devices (TLM C, leading to unreliable  $R_{sh}$  extraction), and an appropriate balance of devices (TLM B). **b**, Example diagram of four-probe measurements to extract  $R_{sh}$ , with a backgate as a demonstration. The channel resistance  $R_{ch}$  between probe 2 and 3 is  $R_{14,23} = V_{23}/I_{14}$ , where  $I_{14}$  is the current flowing from probe 1 to 4 and  $V_{23}$  is the voltage between probe 2 and 3.  $R_{sh} = R_{14,23}$  (W/L).  $R_{sh}$  can be obtained while  $V_{GS}$  is swept, yielding  $R_{sh}$  vs.  $V_{GS}$  or carrier density, which can be used to cross-examine the  $R_{sh}$  extracted from TLM.

Since there can be considerable variation in the quality of emerging semiconducting materials, even on the same chip (e.g., variation in crystal quality in  $MoS_2$ ), this can translate to a sizeable variation in  $R_{sh}$  from one device to another. Note, a perfect TLM is based on the assumption that  $R_{sh}$  is the same for all devices being tested, so any disruption to this assumption translates to inaccuracy in the extraction of  $R_c$ . Hence, it is highly recommended to fabricate several TLM device sets and plot the full distribution of resultant TLM data (multiple data points for each channel length). This provides evidence for how dependable the extraction is; a good example of this is in Ref. <sup>9</sup> and Fig. S5g below.

Another critical aspect of proper TLM data sets is the need for reporting the uncertainties of  $R_{\rm sh}$  and  $R_{\rm c}$  in standard error or confidence interval from a least-squares fit of the TLM curve; an example of this can be seen in Fig.2h and Ref. <sup>10</sup>. Lastly, if a record parameter is claimed based on TLM, four-probe measurements<sup>7,11</sup> should ideally be used as a complementary method to cross-check the results. Traditionally, four-probe measurements are used to characterize the resistivity of "bulk" doped films and a gate bias is not involved. However, to estimate the  $R_{\rm sh}$  for emergent semiconducting materials, it is necessary to sweep the gate bias so that  $R_{\rm sh}$  vs. gate voltage (carrier density,  $n_{\rm S}$ ) can be obtained. An example of the four-probe measurement is given in Fig. S3b. It is key to have probe 2 and 3 placed to the side of the channel so that the voltage probes (2 and 3) do not obstruct the current flow from probe 1 to 4. After obtaining  $R_{\rm sh}$  vs.  $n_{\rm S}$ ,  $R_{\rm c}$  vs.  $n_{\rm S}$  can be derived by subtracting  $R_{\rm sh}$  from  $R_{\rm tot}$ .

A final caution regarding the use of TLM data is regarding the transfer length ( $L_{\rm T}$ ), which is the length of the contact over which the majority of carrier injection occurs between the metal and semiconductor. Traditionally,  $L_{\rm T}$  was also extracted from TLM data as the intercept of the linear fit with the  $L_{\rm ch}$  (x-axis). However, extracting  $L_{\rm T}$  in this manner assumes that the sheet resistance of the semiconductor in the metal-contacted region is the same as for the semiconductor in the channel region. For emergent semiconducting materials, particularly low-dimensional materials like CNTs or 2D TMDs, this is not a valid assumption as transport through the materials happens predominantly (if not entirely) on the surface and is strongly dependent on the materials interfacing with the semiconductor. Because  $L_{\rm T}$  has significant implications for the scalability of the contact length in emergent FETs, it must not be improperly extracted and reported from simple TLM data sets. This is commented on further in the next section (Note S4).

## **Note S4: Additional Parameters**

In the main text, we covered the most representative parameters for reporting and benchmarking emergent FETs. Here we describe some additional parameters used in specific studies.

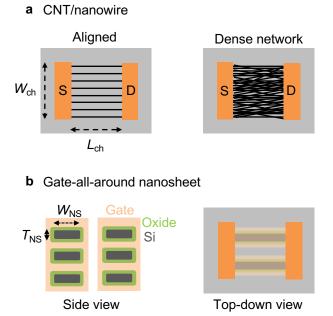

Normalization of  $I_D$  for 1D devices: For 1D or close to 1D devices, to compare  $I_D$ , it is sometimes necessary to convert the  $I_D$  per CNT/nanowire/nanosheet stack to  $I_D$  per  $\mu$ m. If the 1D channel materials are aligned CNTs or nanowires (Fig. S4a), the normalization of currents depends on the density of the 1D channel or the number of 1D channels in 1  $\mu$ m. If the CNTs or nanowire are a dense network, treating the channel similar to a 2D material is more appropriate. For gate-all-around nanosheet devices (Fig. S4b), it is common to report  $I_D$  per nanosheet stack. If reporting the  $I_D$  per channel footprint, then the current per nanosheet stack should be divided by the nanosheet width ( $W_{NS}$ ). A more detailed reporting of  $I_D$  per channel width would require the calculation total channel width of the nanosheets in the stack, which is close to  $W_{NS} \times T_{NS} \times$  number of nanosheets in the stack. The normalized drain currents per channel width is  $I_D$  per stack divided by the total channel width of the stack. Ultimately, what matters is both an indication of what is achieved on a per nanomaterial/structure basis (e.g., per CNT or per nanosheet stack) as well as what is achieved on a per aerial footprint width basis (i.e.,  $\mu$ A per  $W_{ch}$ ).

**Fig. S4** | Normalization of currents for transistors based on 1D or close to 1D channel materials. **a**, top-down view of transistors based on CNTs or nanowires in the form of aligned channels and a dense network. **b**, side-view and top-down (aerial) view of gate-all-around nanosheet transistors.

*Schottky barrier height*: For Schottky contacts between metal and semiconductors, the Schottky barrier height determines the efficiency of carrier transport in the contacts. Hence, properly extracting the barrier height is key for comparing different contact engineering approaches. Examples of Schottky barrier extraction can be found in Ref. <sup>3,12–14</sup>, with some variances in the equations and approaches used.

Transfer length ( $L_T$ ): Because charge carriers tend to crowd near the contact edge when transported between the metal contacts and the channel material, only a certain portion of the contacts actively participate in the carrier transport process. The transfer length denotes the distance over which most of the current transfers in the contact. Traditionally,  $L_T$  can be estimated as  $\sqrt{\frac{\rho_c}{\rho_{sh}}}$  from the transfer length method plot, where the  $\rho_c$  is the specific contact resistivity (unit:  $\Omega \cdot \text{cm}^2$ ) and  $\rho_{sh}$  is the sheet resistance underneath the contact (unit:  $\Omega$ /square) – this is discussed in some detail in Note S3 above. However, this estimation is not reliable for emergent transistors due to: 1) many of the emergent transistors use ultra-thin, low-dimensional nanomaterials, which can alter the current crowding behavior; 2) lots of research-grade emergent transistors have gated contacts, which complicates the estimation of the sheet resistance underneath the contact; and 3) the difference in the interface between the metal-semiconductor and gate insulator semiconductor leads to further differences in sheet resistance of the semiconductor in these regions. Hence, accurately determining  $L_T$  will depend on physically scaled contacts to observe the contact scaling behavior.

Interface trap density  $(D_{it})$ : This parameter is essential for studying and evaluating novel gate dielectrics. Different methods for determining  $D_{it}$  can be found in Ref. <sup>12</sup>.

*High-frequency response of the gate insulator capacitance*: Although most of the parameters covered in the main text are low-frequency parameters, for devices to be eventually used in high-frequency and high-performance applications, it is necessary to properly evaluate the high-frequency response of the gate insulator capacitance and the current-voltage characteristics<sup>15</sup>.

## Note S5: Demonstration of device spread and parameter variations

As indicated in the main text, we recommend showing device spread and parameter variations to demonstrate the full picture of the reported devices. In Fig. S5, based on ten TLM structures similar to the one used in Fig. 2, we demonstrate the spread of device characteristics and parameter variations using a cumulative distribution function plot and boxplots.

Fig. S5 | Demonstration of device spread and parameter variations based on ten TLM structures. **a**, Example transfer curves ( $I_D$ - $V_{GS}$ ) for the TLM structure in Fig. 2. **b**, Measured subthreshold curves ( $I_D$ - $V_{GS}$ ) of ten devices with  $L_{ch}$  of 280 nm of 280 nm. **c**, Cumulative distribution function (CDF) of the hysteresis voltage for the ten devices with  $L_{ch}$  of 280 nm. Boxplots of (**d**)  $V_T$ , (**e**)  $I_D$  at  $V_{DS} = 1$  V and  $n_S = 1.3 \times 10^{13}$  cm<sup>-2</sup>, (**f**) the minimal SS extracted near  $I_D = 10$  nA, and (**g**) ten TLM plots with the median  $R_c$  value of 3 kΩ·μm.

## Note S6: Benchmarking devices with different channel thicknesses