## High-performance flexible nanoscale transistors based on transition metal dichalcogenides

Alwin Daus<sup>1</sup>, Sam Vaziri<sup>1</sup>, Victoria Chen<sup>1,4</sup>, Çağıl Köroğlu<sup>1,4</sup>, Ryan W. Grady<sup>1</sup>, Connor S. Bailey<sup>1</sup>, Hye Ryoung Lee<sup>2</sup>, Kirstin Schauble<sup>1</sup>, Kevin Brenner<sup>1</sup> and Eric Pop<sup>1,3</sup> ✓

Two-dimensional (2D) semiconducting transition metal dichalcogenides could be used to build high-performance flexible electronics. However, flexible field-effect transistors (FETs) based on such materials are typically fabricated with channel lengths on the micrometre scale, not benefitting from the short-channel advantages of 2D materials. Here, we report flexible nanoscale FETs based on 2D semiconductors; these are fabricated by transferring chemical-vapour-deposited transition metal dichalcogenides from rigid growth substrates together with nano-patterned metal contacts, using a polyimide film, which becomes the flexible substrate after release. Transistors based on monolayer molybdenum disulfide ( $MoS_2$ ) are created with channel lengths down to 60 nm and on-state currents up to 470  $\mu$ A  $\mu$ m<sup>-1</sup> at a drain-source voltage of 1V, which is comparable to the performance of flexible graphene and crystalline silicon FETs. Despite the low thermal conductivity of the flexible substrate, we find that heat spreading through the metal gate and contacts is essential to reach such high current densities. We also show that the approach can be used to create flexible FETs based on molybdenum diselenide ( $MoSe_2$ ) and tungsten diselenide ( $WSe_2$ ).

he Internet of Things (IoT) envisions electronics physically present in all aspect of our daily lives—providing information about the machines and environment around us, as well our own bodies. Some of the devices required for this can be created with rigid silicon, but there is also a need for electronics with non-planar form factors<sup>1,2</sup>, in other words, devices that are thin and light and can be conformally attached to objects with unusual shapes, on human skin or implanted in the body<sup>1</sup>. This will require nanoscale flexible electronics that are robust to mechanical strain, easy to integrate, and capable of low-power consumption and high performance<sup>2,3</sup>.

Two-dimensional (2D) materials are good candidates for flexible electronics due to their lack of dangling bonds, good electron or hole mobility in atomically thin (sub-1-nm) layers, low short-channel effects and ability to be transferred onto different substrates  $^{2,4-7}$ . In particular, monolayer transition metal dichalcogenides (TMDs) such as MoS $_2$  are well-suited for low-power applications due to their electronic band gaps ( $\sim\!2\,\text{eV})^{8,9}$ , which enable low off-state currents ( $\sim\!f\text{A}\,\mu\text{m}^{-1})^{10,11}$ . However, the development of high-performance flexible TMD field-effect transistors (FETs) with nanoscale features is challenging because of difficulties creating such small channel lengths on flexible substrates  $^{12}$ , as well as the fact that the TMD transfer process can lead to contamination or damage of the atomically thin material  $^{13-15}$ .

The shortest flexible  $MoS_2$  transistors reported so far, which had channel lengths of ~68 nm, used three-layer exfoliated material and had on-state currents of  $135\,\mu\text{A}\,\mu\text{m}^{-1}$ , probably limited by their contact resistance<sup>16</sup>. Currently, for large-scale practical applications,  $MoS_2$  must be synthesized by chemical vapour deposition (CVD). The shortest channel length reported for devices based on CVD  $MoS_2$  is ~750 nm (with a gate length of ~500 nm) with  $85\,\mu\text{A}\,\mu\text{m}^{-1}$  on-state current, which is also contact-limited<sup>17</sup>. Beyond  $MoS_2$ , there have also been some reports on flexible transistors based on other TMDs, such as  $WSe_2^{18-21}$ . Importantly, achieving a high

transistor on-state current requires both short channels and low contact resistance, for example, by doping the TMD<sup>22,23</sup> and optimizing the metal–TMD interface<sup>24,25</sup>.

In this Article, we report flexible monolayer MoS<sub>2</sub> transistors with on-state currents up to  $\sim\!470\,\mu\text{A}\,\mu\text{m}^{-1}$  at drain–source voltage  $V_{\rm DS}=1\,\rm V$  in sub-100-nm channels. The devices are created by transferring the TMDs together with lithographically predefined metal contacts onto flexible substrates. The TMD is grown using CVD on a SiO<sub>2</sub>/Si substrate and the critical contact separation is defined while the channel is still on the rigid substrate, enabling the fabrication of nanoscale devices. Flexible polyimide (PI) is spin-coated onto the pre-patterned structures and they are released together, with the remaining process continuing on the PI. The approach is also used to create flexible FETs based on MoS<sub>2</sub>, WSe<sub>2</sub> and MoSe<sub>2</sub>, all of which have staggered device configurations<sup>26</sup>: that is, the channel is sandwiched between the source/drain and the gate.

#### Transfer process with embedded contacts

The TMDs were grown by CVD on SiO<sub>2</sub>/Si substrates as previously reported<sup>27-30</sup>. Information on substrate preparation and MoS<sub>2</sub> properties, including Raman, photoluminescence (PL), atomic-force microscopy and layer homogeneity, is provided in Supplementary Sections 1 and 2, and details about the Au liftoff process are given in the Methods. Subsequently, we lithographically patterned Au metal contacts on top. We chose Au without an adhesion layer because of its good contact resistance<sup>24</sup> (R<sub>C</sub>) to MoS<sub>2</sub> and its low adhesion to SiO<sub>2</sub><sup>31</sup>. Both the Au and TMD (lacking out-of-plane dangling bonds) can be released from the SiO<sub>2</sub> surfaces without damage, as shown below. After the contacts were defined, we conformally covered the pre-patterned structures with ~5 µm of PI, which was released, together with the TMD and Au, from the SiO<sub>2</sub>/Si growth substrate by immersion and agitation in deionized (DI) water (Methods). Although performing the entire device fabrication before transfer could be envisaged, most dielectrics will stick to the SiO<sub>2</sub> substrate

<sup>1</sup>Department of Electrical Engineering, Stanford University, Stanford, CA, USA. <sup>2</sup>Geballe Laboratory for Advanced Materials, Stanford University, Stanford, CA, USA. <sup>3</sup>Department of Materials Science & Engineering, Stanford University, Stanford, CA, USA. <sup>4</sup>These authors contributed equally: Victoria Chen, Çağıl Köroğlu. <sup>™</sup>e-mail: epop@stanford.edu

ARTICLES NATURE ELECTRONICS

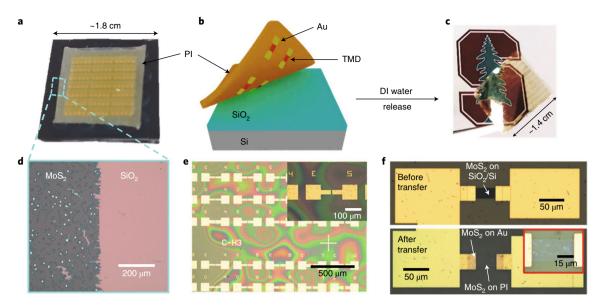

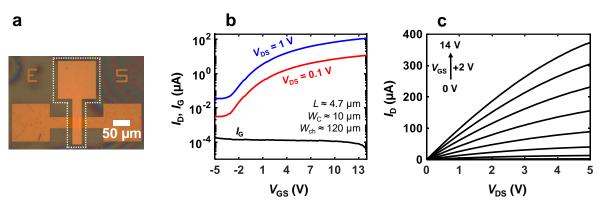

**Fig. 1 | Transfer process for 2D monolayers with contacts. a**, Optical image of  $MoS_2$  and patterned metal, covered by PI, on  $SiO_2/Si$ . **b**, Schematic of the transfer process. The PI with embedded metal contacts and monolayer TMD are released from the rigid growth substrate. **c**, Optical image of the flexible PI after transfer. **d-f**, Optical microscope images of the  $SiO_2/Si$  growth substrate left behind after transfer (with the bare  $SiO_2$  surface where  $SiO_2$  had been previously covered by PI) (**d**), the PI film with contacts and unpatterned  $SiO_2$  after transfer (**e**) and contacts with patterned  $SiO_2/Si$  (**f**, top) and PI (**f**, bottom). Insets show close-ups of FET channels. Raman and PL spectra of  $SiO_2/Si$  and  $SiO_2/Si$  in Supplementary Section 4.

and complicate the release procedure. Thus, we decided to continue processing the gate stack after transfer to the PI substrate (as further described below and in the Methods).

Figure 1a shows the SiO<sub>2</sub>/Si substrate with TMD, contacts and PI, Fig. 1b displays the release schematic and Fig. 1c shows the transparent PI substrate after release. We note that a similar damage-free transfer of MoS<sub>2</sub> layers (without contacts) for coplanar<sup>26</sup> micrometre-sized FETs has recently been demonstrated over 4-inch wafers<sup>32</sup>, indicating that this approach could be scaled up. The optical image in Fig. 1d shows that the TMD (here MoS<sub>2</sub>) is completely delaminated from the area that had been covered by PI on the SiO<sub>2</sub>/Si substrate. Note that agitation in DI water also causes some delamination of MoS, in the area that is not covered by PI (for example, at the bottom left and edges). We can transfer continuous (Fig. 1e) as well as pre-patterned (Fig. 1f) MoS, films with embedded contacts, enabling us to realize devices based on a number of fabrication approaches. As shown later, we have fabricated FETs with MoS<sub>2</sub>, MoSe<sub>2</sub> and WSe<sub>2</sub>, where only the contacts were patterned before transfer, minimizing the process steps on unprotected TMDs (Fig. 1e and Supplementary Section 3), but leading to channel widths greater than the electrode widths (referred to as type A devices). We also realized FETs where the MoS<sub>2</sub> channel was predefined by reactive ion etching (RIE) before transfer (Fig. 1f), which enables accurate channel width definition (referred to as type B). Further details on device fabrication are provided in the Methods.

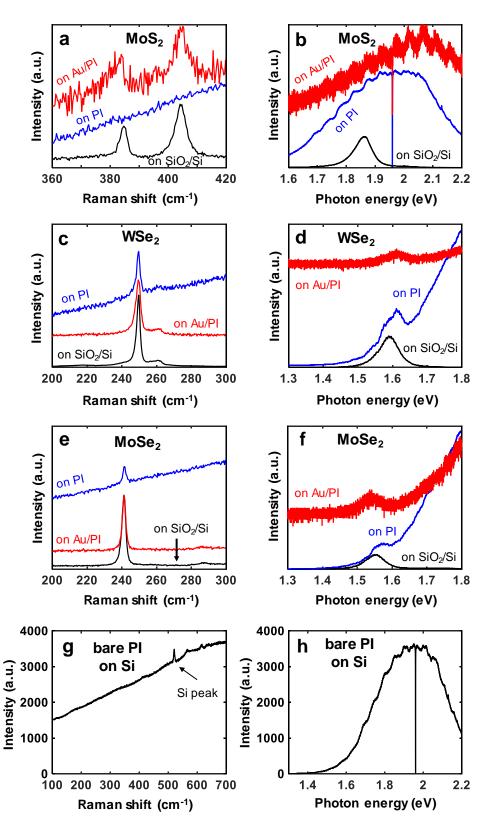

To confirm that the TMDs remain intact throughout the transfer process, we performed extensive Raman spectroscopy and PL measurements before and after transfer (Supplementary Section 4). We observe that the PI background signal and quenching on Au surfaces<sup>33,34</sup> affect the resolution and visibility of TMD peaks. The Raman and PL spectra on SiO<sub>2</sub>/Si indicate TMDs with monolayer thickness; however, MoSe<sub>2</sub> also had regions with bilayers (Supplementary Section 4). Generally, the absence of major changes in the Raman and PL results before and after transfer indicates that mono- as well as multilayer TMDs can be readily transferred with this technique, without apparent damage. In addition, we found that the surface roughness does not discernibly increase after transfer, preserving

root-mean-square roughness below 0.5 nm (Supplementary Section 2). The electrical results presented in the following further confirm the excellent viability of this transfer approach.

#### Flexible top-gated FETs

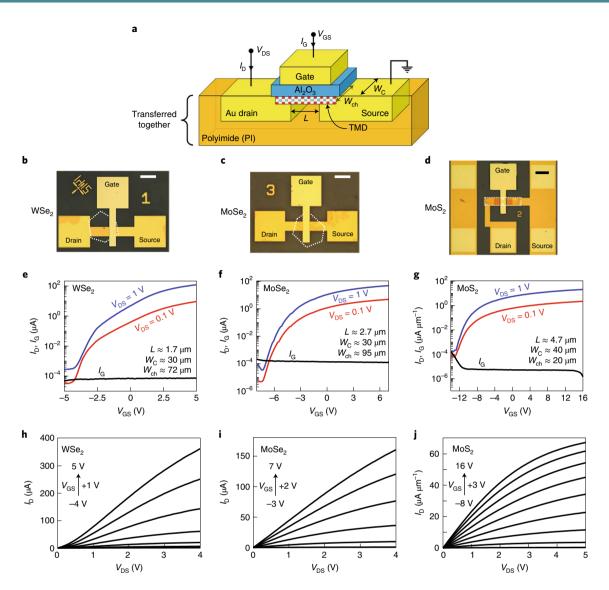

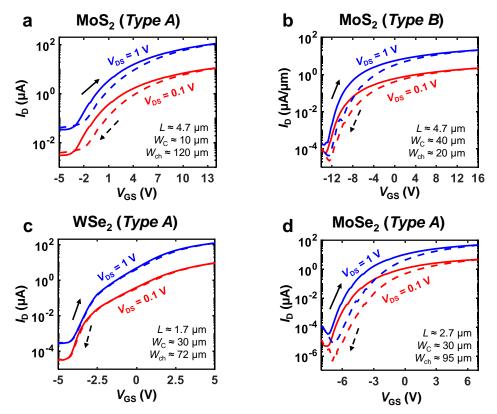

After the transfer process, the material stack was flipped with the source and drain contacts embedded in the PI substrate and the TMD semiconductor on top. To prevent contamination of this exposed TMD surface, we deposited an Al<sub>2</sub>O<sub>3</sub> gate dielectric immediately after the transfer process and before any other patterning steps. The fabrication process was finalized with gate metal definition, leading to a staggered device geometry. For MoS, FETs of type A, we used RIE to pattern the channel and gate dielectric together, after gate metal deposition, but channels of type B devices were already patterned by RIE before transfer (additional fabrication details are provided in the Methods). The device cross-section is schematically shown in Fig. 2a, and Fig. 2b-d displays optical images of the WSe<sub>2</sub>, MoSe<sub>2</sub> and MoS<sub>2</sub> FETs. Measured transfer and output characteristics of micrometre-scale FETs with WSe<sub>2</sub>, MoSe<sub>2</sub> (both type A) and MoS<sub>2</sub> (type B) are presented in Fig. 2e-j, respectively. All display n-type behaviour, because electron conduction is typically dominant for evaporated Au contacts to these materials<sup>20,35</sup>.

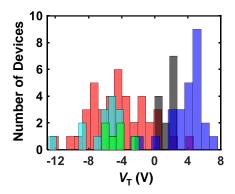

The extracted device parameters for all TMDs are listed in Table 1. Threshold voltage ( $V_{\rm T}$ ) and extrinsic field-effect mobility ( $\mu_{\rm FE,ext}$ ) were estimated at the maximum transconductance ( $g_{\rm m}$ ), using the measured Al<sub>2</sub>O<sub>3</sub> gate oxide capacitance ( $C_{\rm ox}$ =0.21–0.32  $\mu$ F cm<sup>-2</sup>) from the TMD FETs obtained in accumulation (Supplementary Section 5)<sup>36</sup>. The ~1.7- $\mu$ m-long monolayer WSe<sub>2</sub> FET exhibits a maximum on-state current of  $I_{\rm D}$ =3.6±0.1  $\mu$ A  $\mu$ m<sup>-1</sup> (the source of the error bars is explained below) at a drain–source voltage of  $V_{\rm DS}$ =1 V, which is over twice larger than the highest previously reported for flexible WSe<sub>2</sub> (using bilayer exfoliated material)<sup>18</sup>. The ~2.7- $\mu$ m-long MoSe<sub>2</sub> FET reaches  $I_{\rm D}$ =4.2±0.4  $\mu$ A  $\mu$ m<sup>-1</sup> at  $V_{\rm DS}$ =4 V, which is also a clear demonstration of flexible MoSe<sub>2</sub> FETs.

The mobility and width-normalized current of type A devices are listed with error bars because their channel width was not patterned and they were subject to (some) current spreading effects, NATURE ELECTRONICS ARTICLES

**Fig. 2** | **Flexible FETs** with **TMDs. a**, Schematic cross-section. **b-d**, Optical microscope images of FETs with WSe<sub>2</sub> (type A) (**b**), MoSe<sub>2</sub> (type A) (**c**) and MoS<sub>2</sub> (type B) (**d**). The white dotted lines mark the outline of the 2D materials. Scale bars, 50  $\mu$ m. **e-j**, Measured transfer and output characteristics of WSe<sub>2</sub> (type A) (**e,h**), MoSe<sub>2</sub> (type A) (**f,i**) and MoS<sub>2</sub> (type B) (**g,j**). Red and blue lines in **e-g** represent drain current,  $I_D$ . The gate current ( $I_G$ ) is often negligible, although for some devices it can limit the on/off ratio.

which we account for with numerical simulations (Supplementary Section 15). For example, the unpatterned hexagonal crystals for the Se-based FETs are shown in Fig. 2b,c. Their measured data are shown in plain current units ( $\mu$ A) in Fig. 2e,f and Fig. 2h,i, respectively, but the error bars are included when presenting their width-normalized current ( $\mu$ A  $\mu$ m<sup>-1</sup>), for example in Table 1.

The correction is not needed for our type B devices because of the optimized geometry and modified fabrication process. Hence, Fig. 2g,j, for type B MoS<sub>2</sub> FETs, is displayed in width-normalized units and the better quality of this material also enables larger  $I_{\rm D}\approx 67.3\,\mu{\rm A\,\mu m^{-1}}$  in a ~4.7-µm-long FET at  $V_{\rm DS}=5\,\rm V$ . In comparison, type A MoS<sub>2</sub> FETs had higher subthreshold swing (SS) and off-state current, reducing their on/off ratio (Table 1 and Supplementary Section 6). Furthermore, the process flow for type B devices facilitates the fabrication of circuits, and an example inverter is shown in Supplementary Section 7. Comparing device hysteresis<sup>37</sup>, we find it ranges from ~0.1 V (WSe<sub>2</sub>) to ~1.6 V (MoSe<sub>2</sub>) for all devices and TMDs, indicating that the additional patterning step of type B devices does not deteriorate TMD interfaces

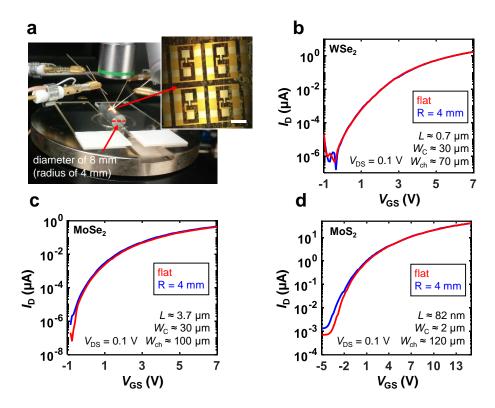

(Supplementary Section 8). We have also verified the stability of the flexible TMD FETs under tensile bending and found no notable changes for a bending radius of  $4 \, \mathrm{mm}$  or a tensile strain of  $\sim 0.063\%$  (Supplementary Section 9).

#### Nanoscale flexible MoS<sub>2</sub> transistors

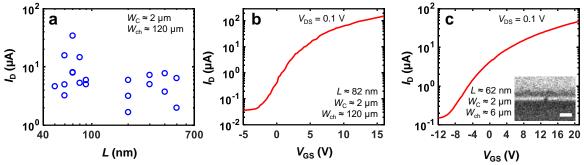

As  $MoS_2$  has the most mature growth process with the highest electrical quality and best surface coverage, we further studied its FET scaling down to  $\sim\!60\,\mathrm{nm}$  (Supplementary Section 10) with electron-beam lithography (EBL) for source–drain contact patterning. Importantly, this nanoscale resolution is enabled by our approach, wherein the contact patterning is first performed on the atomically smooth  $\mathrm{SiO}_2/\mathrm{Si}$  surface instead of the PI, which is prone to waviness, enhanced charging effects and possible damage in  $\mathrm{EBL}^{38}$ . We also verified that this process is benign to  $\mathrm{MoS}_2$ , performing Raman and PL measurements before and after EBL, finding no apparent evidence of damage to the  $\mathrm{MoS}_2$  (Supplementary Section 11). The remaining device fabrication and transfer were performed as described above.

ARTICLES NATURE ELECTRONICS

| Table 1   Electrical parameters of flexible FETs |                     |                                                                       |                                                                            |                                |                            |                     |

|--------------------------------------------------|---------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------|----------------------------|---------------------|

| Device                                           | Channel length (nm) | $\mu_{\rm FE,ext}$ (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | $I_{\rm D}$ at $V_{\rm DS} = 1 \text{V} (\mu \text{A}  \mu \text{m}^{-1})$ | $V_{\scriptscriptstyle T}$ (V) | SS (mV dec <sup>-1</sup> ) | On/off ratio        |

| <b>WSe<sub>2</sub></b> (type A)                  | 1,700               | 4.1 ± 0.1 <sup>a</sup>                                                | 3.6 ± 0.1 <sup>a</sup>                                                     | 1.6                            | 380                        | 3×10 <sup>5</sup>   |

| MoSe <sub>2</sub> (type A)                       | 2,700               | 1.2 ± 0.1 <sup>a</sup>                                                | 1.3 ± 0.1 <sup>a</sup>                                                     | -2                             | 430                        | 1×10 <sup>6</sup>   |

| MoS <sub>2</sub> (type A)                        | 4,700               | 14.2 ± 2.2 <sup>a</sup>                                               | 5.5 ± 0.9°                                                                 | 3.9                            | 1,700                      | $3.6 \times 10^{3}$ |

| MoS <sub>2</sub> (type B)                        | 4,700               | 24                                                                    | 21                                                                         | -5.2                           | 850                        | 1×10 <sup>5</sup>   |

| MoS <sub>2</sub> (type B)                        | 112                 | 8.1                                                                   | 229                                                                        | 0.6                            | 730                        | 2×10 <sup>6</sup>   |

| MoS <sub>2</sub> (type A)                        | 82                  | 23.2 ± 1.4 <sup>a</sup>                                               | 466 ± 40°                                                                  | 6                              | 1,000                      | 4×10³               |

The extrinsic field-effect mobility  $\mu_{\text{FE,ext}}$  and threshold voltage  $V_{\text{T}}$  were extracted from the maximum  $g_{\text{m}}$  in the linear operating regime at a drain-source voltage  $V_{\text{DS}} = 0.1V$ . The subthreshold swing (SS) value denotes the extracted minimum. We note some  $V_{\text{T}}$  variability, which is not unusual for 2D transistors in academic fabrication facilities. <sup>a</sup>Values corrected for current spreading.

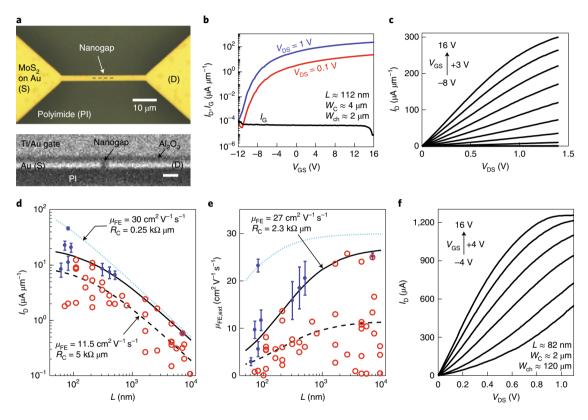

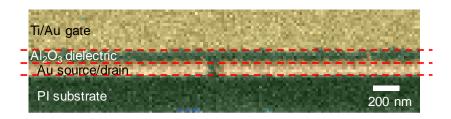

**Fig. 3 | Nanoscale MoS**<sub>2</sub> **FETs. a**, Optical microscope image of a nanoscale channel after transfer (top) and cross-section scanning electron microscopy (SEM) image of a transistor with channel length (L) of ~100 nm (bottom; scale bar, 200 nm). The cross-section is taken along the dashed line in the top image. **b,c**, Transfer (**b**) and output (**c**) characteristics of a type B MoS<sub>2</sub> FET with  $L \approx 112$  nm. **d,e**, Drain current  $I_D$  (**d**) and extrinsic field-effect mobility  $\mu_{FE,ext}$  (**e**) as a function of L for ~50 devices at a drain-source voltage of  $V_{DS} = 0.1$  V and an overdrive voltage of  $V_{GS} - V_T = 8$  V. Solid black and dashed black lines illustrate a fitted trend for 'best' and 'typical' type B devices (red circles), while the blue dotted lines include the best type A device (blue symbols). Error bars of blue symbols represent uncertainty due to corrections for current spreading. **f**, Electrical characteristics of a MoS<sub>2</sub> FET (type A) with  $L \approx 82$  nm, showing remarkably high  $I_D > 1.2$  mA, which is ~470 μA μm<sup>-1</sup> after current spreading correction.

Figure 3a presents a top-view optical image of a nanoscale channel after transfer and a post-fabrication-device cross-section. The cross-section shows that the Al $_2$ O $_3$  gate dielectric covers the planar source and drain electrodes, including the  $\sim$ 100-nm nanogap between them, illustrating the absence of 'steps' in the surface topography enabled by this fabrication technique with contacts embedded in the flexible substrate (Supplementary Section 2). Electrical measurements of a similar type B device with  $\sim$ 112-nm-long channel are shown in Fig. 3b,c, showing a good on/off ratio (>106), high  $I_{\rm D}\approx 303\,\mu{\rm A}\,\mu{\rm m}^{-1}$  (at  $V_{\rm DS}=1.4\,{\rm V}$ ) and  $\mu_{\rm FE,ext}\approx 8.1\,{\rm cm}^2{\rm V}^{-1}\,{\rm s}^{-1}$ . The mobility appears smaller than in micrometre-scale devices due to the greater contribution from  $R_{\rm C}$ , as discussed in the following (for other device parameters see Table 1).

The measured output characteristics (Fig. 3c,f) show signs of self-heating and velocity saturation  $^{23,59}$  due to the onset of current saturation at lower  $V_{\rm DS}$  with higher gate–source voltages  $V_{\rm GS}$ , which is similar to the self-heating of MoS<sub>2</sub> FETs on SiO<sub>2</sub>/Si substrates. We estimate that the temperature of this FET channel exceeds 350 °C at the peak input power in Fig. 3f, but the PI remains below its glass transition temperature because the device heat spreading occurs primarily through the gate stack and contacts (Supplementary Section 12). To gain additional insight into intrinsic device parameters, we extracted  $I_{\rm D}$  (at an overdrive  $V_{\rm ov} = V_{\rm GS} - V_{\rm T} = 8$  V) and  $\mu_{\rm FE,ext}$  for channel lengths from ~60 nm to ~10 µm in Fig. 3d,e. Measuring numerous devices allows us to comment both on 'typical' and 'best-case' device performance. We used a model that relates  $I_{\rm D}$  and  $\mu_{\rm FE,ext}$  to  $L_{\rm T}$

NATURE ELECTRONICS ARTICLES

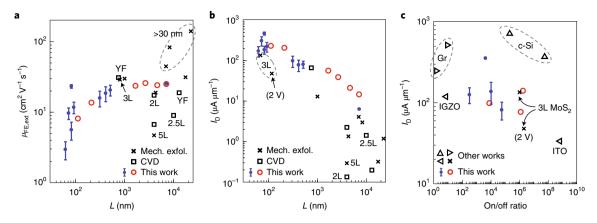

**Fig. 4 | Benchmarking flexible FETs. a,b**, Extrinsic field-effect mobility  $μ_{FE,ext}$  (**a**) and drain current  $I_D$  (at  $V_{DS}$ =1V) (**b**) for flexible MoS₂ transistors as a function of channel length (L)<sup>4,6,17,32,44-53</sup>. Three studies reported  $μ_{FE}$  excluding contact resistance, with the y-function method (YF). A few points correspond to three-layer (3L) MoS₂, one of them at  $V_{DS}$ =2 V, one (L = 68 nm) at unspecified voltage. Most CVD-grown MoS₂ are monolayers (1L); the other thicknesses are as labelled up to five layers (5L), and unlabelled points are all thicker exfoliated channels. All thicknesses and more details from other works are listed in Supplementary Section 16. The MoS₂ films in this work are mostly monolayers with some multilayer islands (up to 34%; Supplementary Section 1). **c**, Reported  $I_D$  (at  $V_{DS}$ =0.5 V) versus on/off current ratio for flexible FETs with channel L ≤200 nm (refs. <sup>43,54-58</sup>). For comparison, two data points are shown for graphene (Gr), two for crystalline silicon (c-Si), two for oxide semiconductors (indium tin oxide (ITO) and indium gallium zinc oxide (IGZO)) and the others for MoS₂ (our CVD monolayer data and two reports on 3L exfoliated). Blue and red symbols are type A and B devices from this work, respectively. Error bars on blue symbols represent uncertainty from current spreading correction.

$R_{\rm C}$  and the intrinsic field-effect mobility  $\mu_{\rm FE}$ . (The adapted model<sup>40</sup>, the  $V_{\rm T}$  and  $\mu_{\rm FE,ext}$  extractions are described in Supplementary Sections 5 and 14.) Figure 3d,e shows that  $I_{\rm D}$  plateaus and  $\mu_{\rm FE,ext}$  decreases at sub-1-µm channel lengths, which clearly indicates that these devices are limited by  $R_{\rm C}$ . The dashed black lines show the model for 'typical' type B devices (red circles), which we fitted with an average  $\mu_{\rm FE}$  (~11.5 cm² V<sup>-1</sup> s<sup>-1</sup>) for micrometre-scale devices where the impact of  $R_{\rm C}$  is small, and by setting  $R_{\rm C}$  = 5 k $\Omega$  µm to follow the middle of the distribution for shorter L.

The solid black lines in Fig. 3d,e are based on a similar approach but using higher  $\mu_{EE}$  (~27 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>) to fit the best-performing type B devices with  $R_c = 2.3 \text{ k}\Omega \mu \text{m}$ . Also taking into account the 'best' type A devices (blue symbols and error bars, corrected for current spreading), we fit  $R_C \approx 250 \,\Omega$  µm for one device (at  $L \approx 82 \,\text{nm}$ ) and a slightly higher  $\mu_{\rm FE} = 30 \,\rm cm^2 V^{-1} \,\rm s^{-1}$ , generating the blue dotted lines. The FET with highest on-state current achieves an impressive  $I_D = 466 \pm 40 \,\mu\text{A}\,\mu\text{m}^{-1}$ at  $V_{\rm DS}$ =1V (Supplementary Section 13 provides electrical data and Supplementary Section 15 the current spreading correction), and its electrical characteristics are shown in Fig. 3f and Supplementary Fig. 22b. The presence of a 'hero' device is not surprising when dozens (or hundreds<sup>28</sup>) of devices are measured, being both an indicator of academic fabrication and growth variability, and of the promise of these 2D semiconductors if variability challenges are eventually mitigated by industrial optimization. (We note that our type A and B devices have similar variability; Supplementary Section 13.)

Our estimated best-case  $\mu_{\rm FE}$  and  $R_{\rm C}$  are comparable to the best reported values for monolayer MoS<sub>2</sub> on flexible substrates and on SiO<sub>2</sub>/Si rigid substrates, respectively<sup>17,28,39</sup>. The highest on-state current,  $I_{\rm D}$ , is over three times greater than in previous reports for flexible MoS<sub>2</sub> FETs<sup>16</sup>, similar to the best TMD FETs on rigid substrates<sup>41</sup>, and even comparable to flexible FETs based on graphene<sup>42</sup> and crystalline Si (c-Si)<sup>43</sup>. Moreover, this fabrication technique enables us to scale flexible MoS<sub>2</sub> FETs to the shortest channel lengths reported so far (Supplementary Fig. 22c).

Figure 4 displays benchmarking of our flexible MoS<sub>2</sub> transistors compared to other technologies on flexible substrates. Displaying the extrinsic mobility  $\mu_{\text{FE,ext}}$  and drain current  $I_{\text{D}}$  (at  $V_{\text{DS}} = 1$  V, unless noted otherwise) for flexible MoS<sub>2</sub> FETs versus L (Fig. 4a,b) reveals that nanoscale devices have received little attention until now (values are listed in Supplementary Table 2)<sup>4,16,17,32,44-53</sup>. Figure 4c compares

the on-state current and on/off ratio of the few existing sub-200-nm flexible FETs (at  $V_{\rm DS} = 0.5$  V, unless noted otherwise), showing the good performance of our MoS<sub>2</sub>, even next to high-mobility materials (values are listed in Supplementary Table 3)<sup>43,54–58</sup>. The on/off ratio of MoS<sub>2</sub> is many orders of magnitude higher than graphene (on/off <10), making MoS<sub>2</sub> more suitable for low-power applications among existing 2D channel materials. Compared to flexible c-Si FETs, flexible TMD FETs have a fundamentally different structure, with a sub-nanometre thin channel without out-of-plane dangling bonds. This enables shorter channel lengths, better mechanical robustness and potentially lower cost (due to the simple transfer processes), all of which are advantageous for higher-performance and lower-power operation on flexible substrates.

#### Conclusions

We have reported high-performance MoS, transistors on flexible substrates, created using a transfer process that includes nano-patterned contacts. The approach allows devices with channel lengths as low as ~60 nm to be fabricated. Our devices exhibit drive currents up to  $\sim 470 \,\mu\text{A}\,\mu\text{m}^{-1}$  at  $V_{DS} = 1 \,\text{V}$ , among the highest for any monolayer 2D semiconductor, including those on rigid Si substrates. The on-state current is also comparable to those of flexible graphene and c-Si transistors, while maintaining an on/off current ratio over 104. The high current is achieved despite the low thermal conductivity of the PI substrate, as the short channel devices benefit from heat spreading through the gate and contacts. We have also shown that the fabrication technique can be applied to other 2D semiconductors, creating flexible MoSe<sub>2</sub> and monolayer WSe<sub>2</sub> FETs. Our approach could be used as a template for making flexible transistors with other materials that have few demonstrations of short-channel devices, including oxides, organics and carbon nanotubes. Together with further optimization of electrostatic control (such as thinner gate dielectrics or double gates) and reduced parasitics (such as lower parasitic capacitance; Supplementary Section 17), the technique could allow flexible TMD electronics to be incorporated into low-power and high-performance IoT applications.

#### Methods

**Raman and PL measurements.** The Raman and PL measurements were performed on a HORIBA Scientific LabRAM HR Evolution spectrometer using an excitation

ARTICLES NATURE ELECTRONICS

wavelength of 532 nm. For the Raman measurements on  $SiO_2/Si$ , for acquisition time, accumulations, laser power and optical grating we used 5 s, 3, 0.14 mW and 1,800 gr mm<sup>-1</sup>, and the spot size was less than 1 µm. For the Raman measurements after transfer on PI or Au/PI surfaces, the acquisition time was increased to 45 s, while the other parameters remained the same. For PL measurements on  $SiO_2/Si$ , PI and Au/PI, the acquisition time, accumulations, laser power and optical grating were 5 s, 3, 0.14 mW, 600 gr mm<sup>-1</sup>.

${\bf Device\ fabrication\ including\ transfer\ process\ and\ lift off\ procedure.}\ {\it Fabrication}$ of type A devices, channel defined last. The TMDs were grown on Si/SiO<sub>2</sub> substrates with CVD, as previously reported<sup>27-30</sup>. For device fabrication, 45-nm-thick Au source and drain contacts were first deposited by electron-beam evaporation and patterned by liftoff. Optionally, the adhesion of metal contacts to the subsequently spin-coated PI could be improved by evaporating an additional Ti layer on top of the Au before liftoff, but we have not observed discernible differences in transfer efficacy by doing so. The lithographic patterning for that step was carried out using optical lithography (Heidelberg MLA 150 direct write lithography tool) for micrometre-scale channel lengths, and via EBL for sub-micrometre-scale channel lengths (parameters are listed in the following). Then, ~5-µm-thick PI (PI-2610, HD MicroSystems) was spin-coated on top, baked at 90 °C and 150 °C on a hot plate, each for 90 s, and finally cured in a nitrogen oven at 250 °C for 30 min. Before PI spin-coating, the outside edges of the silicon substrate were protected with tape to facilitate the release of PI from the Si substrate (Fig. 1a). The transfer was performed in DI water by initially mechanically releasing the outside edges with a tweezer followed by agitation until the PI substrate (with the metal contacts and TMD) floated on the DI water surface. After nitrogen blow-drying the substrate, a 1.5-nm-thick Al blanket film was deposited on top by electron-beam evaporation. This film acts as a seed layer for the subsequent atomic-layer deposition of an Al<sub>2</sub>O<sub>3</sub> gate dielectric at 200 °C. Note that we used 35-nm Al<sub>2</sub>O<sub>3</sub> for the MoS<sub>2</sub> devices and 23-nm-thick Al<sub>2</sub>O<sub>3</sub> for the MoSe<sub>2</sub> and WSe<sub>2</sub> devices. This yields  $C_{ox} \approx 0.21-0.32 \,\mu\text{F} \,\text{cm}^{-2}$ , as directly measured in Supplementary Fig. 12. The oxide thicknesses were chosen to ensure higher device yield and to have numerous FETs for measurement. After the atomic-layer deposition, the gate metal was deposited by electron-beam evaporation of Ti/ Au (5/60 nm) and patterned by optical lithography and liftoff. This concluded the fabrication for MoSe<sub>2</sub> and WSe<sub>2</sub> devices. For MoS<sub>2</sub> devices, as a final step, the Al<sub>2</sub>O<sub>3</sub> and MoS<sub>2</sub> were patterned together using RIE (Oxford 80 RIE) in CF<sub>4</sub>:O<sub>2</sub> at gas flows of 50 s.c.c.m.:5 s.c.c.m., power of 150 W and a pressure of 30 mtorr.

Fabrication of type B devices, channel defined before transfer. Up to the source and drain contact metallization, the fabrication of the type B device is the same as for the type A device. However, after source and drain metallization, the MoS<sub>2</sub> channels were patterned by RIE (Oxford 80 RIE) in CF<sub>4</sub>:O<sub>2</sub> at gas flows of 50 s.c.c.m.:10 s.c.c.m., power of 100 W and pressure of 30 mtorr, followed by surface cleaning with O<sub>2</sub> plasma (20 W, 10 mtorr, 40 s.c.c.m.) in the same tool. Then, contact pads and leads were defined by optical lithography, electron-beam evaporation of Au/Ti (60 nm/5 nm) and liftoff (a Ti layer on top of Au is optional, as discussed for the type A fabrication). This was followed by PI spin-coating, curing and transfer of all structures in the same way as described for the type A devices. After gate dielectric deposition (same as for the type A devices), via holes for probing, source and drain electrodes were wet-etched in Al etchant at 40 °C. Finally, the gate metallization was performed similarly as for the type A devices.

Liftoff procedure. The source and drain contacts in this work consist of bare Au, which is known to have poor adhesion, especially to SiO231. Thus, we needed to perform this step carefully to avoid delamination of the electrodes. The procedure is the same for liftoff after optical lithography and after EBL. In both cases, we used a double layer of resist (LOL2000 and SPR3612 from Shipley for optical lithography; see next section for EBL), which provided an undercut in the resist stack. Thus, the Au, which was evaporated on top of the entire sample, is disconnected over the resist steps. This is important, because we wish to avoid strong mechanical forces (for example, no sonication), which could delaminate either the Au or the TMD. After the Au was evaporated on top of the resist stack, we soaked the samples for >12 h in *N*-methyl pyrrolidone (for optical lithography) or acetone (for EBL). The Au was then gently removed from undesired locations by pulsing the solvent over the sample surface with a pipette. This step lifted off most metal (>95% by visual inspection), but to remove remaining stubborn metal residue, the samples were immersed in acetone followed by isopropanol, and gentle solvent pulsing with a pipette was applied in each solvent. Finally, the samples were removed from the isopropanol and nitrogen blow-dried.

**EBL on MoS**<sub>2</sub>. We used a double layer of poly(methyl methacrylate) (PMMA) for liftoff patterns defined by EBL. The bottom and top layer were 50-nm-thick 495 K A2 PMMA and 200-nm-thick 950 K A4 PMMA, respectively. EBL was performed on a JEOL JBX 6300 lithography system at a dose of 900  $\mu C\,cm^{-2}$  and an acceleration voltage of 100 kV.

**Electrical measurements.** All transistors were tested with a Keithley 4200 system on a probe station in ambient air. For the bending experiments, the substrates were attached to a metallic cylindrical rod with a radius of 4 mm.

#### Data availability

The data that support the plots within this paper and other findings of the study are available from the corresponding author upon reasonable request.

Received: 8 September 2020; Accepted: 7 May 2021; Published online: 17 June 2021

#### References

- He, J., Nuzzo, R. G. & Rogers, J. A. Inorganic materials and assembly techniques for flexible and stretchable electronics. *Proc. IEEE* 103, 619–632 (2015).

- Akinwande, D., Petrone, N. & Hone, J. Two-dimensional flexible nanoelectronics. *Nat. Commun.* 5, 5678 (2014).

- Myny, K. The development of flexible integrated circuits based on thin-film transistors. Nat. Electron. 1, 30–39 (2018).

- Salvatore, G. A. et al. Fabrication and transfer of flexible few-layers MoS<sub>2</sub> thin film transistors to any arbitrary substrate. ACS Nano 7, 8809–8815 (2013).

- Gurarslan, A. et al. Surface-energy-assisted perfect transfer of centimeter-scale monolayer and few-layer MoS<sub>2</sub> films onto arbitrary substrates. ACS Nano 8, 11522–11528 (2014).

- Nourbakhsh, A. et al. MoS<sub>2</sub> field-effect transistor with sub-10-nm channel length. Nano Lett. 16, 7798–7806 (2016).

- Liu, H., Neal, A. T. & Ye, P. D. Channel length scaling of MoS<sub>2</sub> MOSFETs. ACS Nano 6, 8563–8569 (2012).

- Gusakova, J. et al. Electronic properties of bulk and monolayer TMDs: theoretical study within DFT framework (GVJ-2e method). *Phys. Status Solidi* (a) 214, 1700218 (2017).

- Ryou, J., Kim, Y.-S., Santosh, K. & Cho, K. Monolayer MoS<sub>2</sub> bandgap modulation by dielectric environments and tunable bandgap transistors. Sci. Rep. 6, 29184 (2016).

- 10. Kshirsagar, C. U. et al. Dynamic memory cells using  $MoS_2$  field-effect transistors demonstrating femtoampere leakage currents. ACS Nano 10, 8457–8464 (2016).

- 11. Illarionov, Y. Y. et al. Annealing and encapsulation of CVD-MoS<sub>2</sub> FETs with 10<sup>10</sup> on/off current ratio. In *Proc. 2018 76th Device Research Conference* (*DRC*) https://doi.org/10.1109/DRC.2018.8442242 (IEEE, 2018).

- Münzenrieder, N., Cantarella, G. & Petti, L. Fabrication and AC performance of flexible indium–gallium–zinc–oxide thin-film transistors. ECS Trans. 90, 55–63 (2019).

- Pu, J. et al. Highly flexible MoS<sub>2</sub> thin-film transistors with ion gel dielectrics. Nano Lett. 12, 4013–4017 (2012).

- 14. Ma, D. et al. A universal etching-free transfer of MoS<sub>2</sub> films for applications in photodetectors. *Nano Res.* **8**, 3662–3672 (2015).

- Zhang, T. et al. Clean transfer of 2D transition metal dichalcogenides using cellulose acetate for atomic resolution characterizations. ACS Appl. Nano Mater. 2, 5320–5328 (2019).

- Cheng, R. et al. Few-layer molybdenum disulfide transistors and circuits for high-speed flexible electronics. Nat. Commun. 5, 5143 (2014).

- Chang, H. Y. et al. Large-area monolayer MoS<sub>2</sub> for flexible low-power RF nanoelectronics in the GHz regime. Adv. Mater. 28, 1818–1823 (2016).

- Das, S., Gulotty, R., Sumant, A. V. & Roelofs, A. All two-dimensional, flexible, transparent and thinnest thin film transistor. *Nano Lett.* 14, 2861–2866 (2014).

- Podzorov, V., Gershenson, M., Kloc, C., Zeis, R. & Bucher, E. High-mobility field-effect transistors based on transition metal dichalcogenides. *Appl. Phys. Lett.* 84, 3301–3303 (2004).

- 20. Qiu, H. et al. Simultaneous optical tuning of hole and electron transport in ambipolar WSe<sub>2</sub> interfaced with a bicomponent photochromic layer: from high-mobility transistors to flexible multilevel memories. *Adv. Mater.* **32**, 1907903 (2020).

- Pu, J. et al. Highly flexible and high-performance complementary inverters of large-area transition metal dichalcogenide monolayers. *Adv. Mater.* 28, 4111–4119 (2016).

- Rai, A. et al. Air stable doping and intrinsic mobility enhancement in monolayer molybdenum disulfide by amorphous titanium suboxide encapsulation. *Nano Lett.* 15, 4329–4336 (2015).

- 23. McClellan, C. J., Yalon, E., Smithe, K. K., Suryavanshi, S. V. & Pop, E. High current density in monolayer MoS<sub>2</sub> doped by AlO<sub>x</sub>. ACS Nano 15, 1587–1596 (2021).

- English, C. D., Shine, G., Dorgan, V. E., Saraswat, K. C. & Pop, E. Improved contacts to MoS<sub>2</sub> transistors by ultra-high vacuum metal deposition. *Nano Lett.* 16, 3824–3830 (2016).

- Liu, Y. et al. Approaching the Schottky–Mott limit in van der Waals metal–semiconductor junctions. *Nature* 557, 696–700 (2018).

- Fortunato, E., Barquinha, P. & Martins, R. Oxide semiconductor thin-film transistors: a review of recent advances. Adv. Mater. 24, 2945–2986 (2012).

- Smithe, K. K., English, C. D., Suryavanshi, S. V. & Pop, E. Intrinsic electrical transport and performance projections of synthetic monolayer MoS<sub>2</sub> devices. 2D Mater. 4, 011009 (2017).

NATURE ELECTRONICS ARTICLES

- 28. Smithe, K. K., Suryavanshi, S. V., Muñoz Rojo, M., Tedjarati, A. D. & Pop, E. Low variability in synthetic monolayer  $MoS_2$  devices. *ACS Nano* 11, 8456–8463 (2017).

- Smithe, K. K. et al. Nanoscale heterogeneities in monolayer MoSe<sub>2</sub> revealed by correlated scanning probe microscopy and tip-enhanced Raman spectroscopy. ACS Appl. Nano Mater. 1, 572–579 (2018).

- Chen, J. et al. Plasmon-resonant enhancement of photocatalysis on monolayer WSe<sub>2</sub>. ACS Photonics 6, 787–792 (2019).

- George, M., Bao, Q., Sorensen, I., Glaunsinger, W. & Thundat, T. Thermally induced changes in the resistance, microstructure and adhesion of thin gold films on Si/SiO, substrates. J. Vac. Sci. Technol. A 8, 1491–1497 (1990).

- Shinde, S. M. et al. Surface-functionalization-mediated direct transfer of molybdenum disulfide for large-area flexible devices. *Adv. Funct. Mater.* 28, 1706231 (2018).

- Daus, A. et al. Metal-halide perovskites for gate dielectrics in field-effect transistors and photodetectors enabled by PMMA lift-off process. *Adv. Mater.* 30, 1707412 (2018).

- 34. Bhanu, U., Islam, M. R., Tetard, L. & Khondaker, S. I. Photoluminescence quenching in gold-MoS<sub>2</sub> hybrid nanoflakes. *Sci. Rep.* **4**, 5575 (2014).

- 35. Somvanshi, D., Ber, E., Bailey, C. S., Pop, E. & Yalon, E. Improved current density and contact resistance in bilayer MoSe<sub>2</sub> field effect transistors by AlO<sub>x</sub> capping. ACS Appl. Mater. Interfaces 12, 36355–36361 (2020).

- Knobelspies, S. et al. Geometry-based tunability enhancement of flexible thin-film varactors. *IEEE Electron Device Lett.* 38, 1117–1120 (2017).

- Datye, I. M. et al. Reduction of hysteresis in MoS<sub>2</sub> transistors using pulsed voltage measurements. 2D Mater. 6, 011004 (2019).

- 38. Scholten, K. & Meng, E. Electron-beam lithography for polymer bioMEMS with submicron features. *Microsyst. Nanoeng.* **2**, 16053 (2016).

- Smithe, K. K., English, C. D., Suryavanshi, S. V. & Pop, E. High-field transport and velocity saturation in synthetic monolayer MoS<sub>2</sub>. Nano Lett. 18, 4516–4522 (2018).

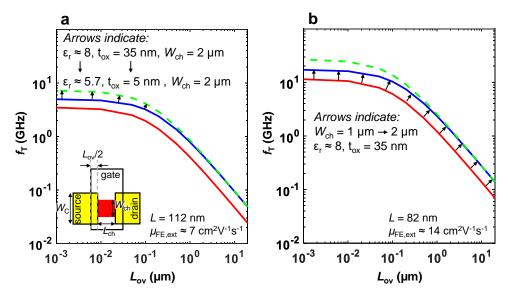

- Münzenrieder, N. et al. Contact resistance and overlapping capacitance in flexible sub-micron long oxide thin-film transistors for above 100-MHz operation. Appl. Phys. Lett. 105, 263504 (2014).

- McClellan, C. J. et al. 2D Device Trends http://2d.stanford.edu (accessed 14 April 2021).

- Lan, Y. et al. Flexible graphene field-effect transistors with extrinsic f<sub>max</sub> of 28 GHz. IEEE Electron Device Lett. 39, 1944–1947 (2018).

- Shahrjerdi, D. et al. Advanced flexible CMOS integrated circuits on plastic enabled by controlled spalling technology. In Proc. 2012 International Electron Devices Meeting (IEDM) 5.1.1–5.1.4 (IEEE, 2012).

- 44. Kwon, H. et al. Selective and localized laser annealing effect for high-performance flexible multilayer MoS<sub>2</sub> thin-film transistors. *Nano Res.* 7, 1137–1145 (2014).

- Chang, H.-Y. et al. High-performance, highly bendable MoS<sub>2</sub> transistors with high-k dielectrics for flexible low-power systems. ACS Nano 7, 5446–5452 (2013)

- 46. Yoon, J. et al. Highly flexible and transparent multilayer  $MoS_2$  transistors with graphene electrodes. Small 9, 3295–3300 (2013).

- Lee, G.-H. et al. Flexible and transparent MoS<sub>2</sub> field-effect transistors on hexagonal boron nitride-graphene heterostructures. ACS Nano 7, 7931–7936 (2013).

- Yoo, G. et al. Real-time electrical detection of epidermal skin MoS<sub>2</sub> biosensor for point-of-care diagnostics. Nano Res. 10, 767–775 (2017).

- Song, W. G. et al. High-performance flexible multilayer MoS<sub>2</sub> transistors on solution-based polyimide substrates. Adv. Funct. Mater. 26, 2426–2434 (2016).

- Ma, J., Choi, K.-Y., Kim, S. H., Lee, H. & Yoo, G. All polymer encapsulated, highly-sensitive MoS<sub>2</sub> phototransistors on flexible PAR substrate. *Appl. Phys. Lett.* 113, 013102 (2018).

- Amani, M., Burke, R. A., Proie, R. M. & Dubey, M. Flexible integrated circuits and multifunctional electronics based on single atomic layers of MoS<sub>2</sub> and graphene. *Nanotechnology* 26, 115202 (2015).

- Woo, Y. et al. Large-area CVD-grown MoS<sub>2</sub> driver circuit array for flexible organic light-emitting diode display. Adv. Electron. Mater. 4, 1800251 (2018).

- Park, Y. J. et al. All MoS<sub>2</sub>-based large area, skin-attachable active-matrix tactile sensor. ACS Nano 13, 3023–3030 (2019).

- Zhai, Y., Mathew, L., Rao, R., Xu, D. & Banerjee, S. K. High-performance flexible thin-film transistors exfoliated from bulk wafer. *Nano Lett.* 12, 5609–5615 (2012).

- 55. Park, S. et al. Extremely high-frequency flexible graphene thin-film transistors. *IEEE Electron Device Lett.* **37**, 512–515 (2016).

- Yeh, C.-H. et al. Gigahertz flexible graphene transistors for microwave integrated circuits. ACS Nano 8, 7663–7670 (2014).

- Wang, M. et al. High performance gigahertz flexible radio frequency transistors with extreme bending conditions. In *Proc. 2019 IEEE International Electron Devices Meeting (IEDM)* 8.2.1–8.2.4 (IEEE, 2019).

- Münzenrieder, N. et al. Focused ion beam milling for the fabrication of 160-nm channel length IGZO TFTs on flexible polymer substrates. Flex. Print. Electron. 5, 015007 (2020).

#### Acknowledgements

A.D. is in part supported by the Swiss National Science Foundation's Early Postdoc. Mobility fellowship (grant no. P2EZP2\_181619) and in part by Beijing Institute of Collaborative Innovation (BICI). R.W.G., C.S.B. and K.S. acknowledge the National Science Foundation (NSF) Graduate Research Fellowship. K.S. also acknowledges support from the Stanford Graduate Fellowship. We thank the Stanford Nanofabrication Facility and Stanford Nano Shared Facilities for enabling device fabrication and characterization, funded under NSF award no. ECCS-1542152. E.P. and S.V. acknowledge support from the Stanford SystemX Alliance.

#### **Author contributions**

A.D. conceived the work and performed the device fabrication and characterization. A.D. and S.V. developed the TMD transfer process. R.W.G. performed the MoS<sub>2</sub> CVD growth and C.S.B. the WSe<sub>2</sub> and MoSe<sub>2</sub> CVD growths. V.C. carried out the electron beam lithography and atomic-force microscopy. A.D. and K.S. performed optical material analysis with help from K.B. H.R.L. carried out scanning electron microscopy. C.K. set up numerical current spreading simulations and thermal simulations with E.P. A.D. analysed all data and wrote the manuscript with help from V.C., C.K. and E.P. All authors revised and commented on the manuscript. E.P. supervised the work.

#### **Competing interests**

The authors declare no competing interests.

#### Additional information

**Supplementary information** The online version contains supplementary material available at https://doi.org/10.1038/s41928-021-00598-6.

Correspondence and requests for materials should be addressed to E.P.

**Peer review information** *Nature Electronics* thanks Henry Medina and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Reprints and permissions information is available at www.nature.com/reprints.

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

© The Author(s), under exclusive licence to Springer Nature Limited 2021

### **Supplementary information**

# High-performance flexible nanoscale transistors based on transition metal dichalcogenides

In the format provided by the authors and unedited

#### **Supplementary Information**

## High-performance flexible nanoscale transistors based on transition metal dichalcogenides

Alwin Daus<sup>1</sup>, Sam Vaziri<sup>1</sup>, Victoria Chen<sup>1,†</sup>, Çağıl Köroğlu<sup>1,†</sup>, Ryan W. Grady<sup>1</sup>, Connor S. Bailey<sup>1</sup>, Hye Ryoung Lee<sup>2</sup>, Kirstin Schauble<sup>1</sup>, Kevin Brenner<sup>1</sup> and Eric Pop<sup>1,3,\*</sup>

#### 1. MoS<sub>2</sub> film properties, growth conditions, SiO<sub>2</sub>/Si substrate preparation

MoS<sub>2</sub> was synthesized by CVD growth as described in prior work.<sup>27,28</sup> The SiO<sub>2</sub>/Si substrates were pretreated by hexamethyldisilazane (HMDS) vapor to provide a hydrophobic surface for the subsequently applied seeding promoter (PTAS, i.e. perylene-3,4,9,10 tetracarboxylic acid tetrapotassium salt dissolved in DI water and dried on a hot plate) on the edges of the chip, which prevents spreading towards the chip center. The same substrate treatments were applied for the growth of the other TMDs. The MoS<sub>2</sub> growth from solid precursors (MoO<sub>3</sub> and S) then forms large single crystal triangles with sizes in the order of tens of microns which coalesce into a continuous film in the chip center, and non-continuous areas closer to the chip edge (see Fig. 1 in previous work<sup>27</sup>).

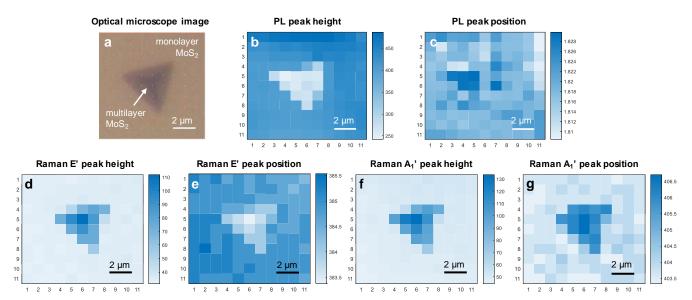

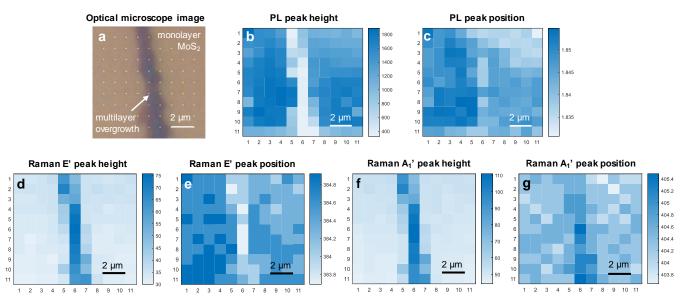

Although the MoS<sub>2</sub> film can essentially be characterized as a monolayer film, some small multilayer islands and overgrowth are present at grain boundaries or nucleation sites. Supplementary Fig. 1 and 2 display Raman and photoluminescence (PL) mapping of a multilayer region and grain boundary, respectively, each surrounded by monolayer MoS<sub>2</sub>. As visible from the peak positions, the Raman peak separation is increased in these multilayer regions suggesting a thickness of about 2-3 MoS<sub>2</sub> layers.<sup>59</sup>

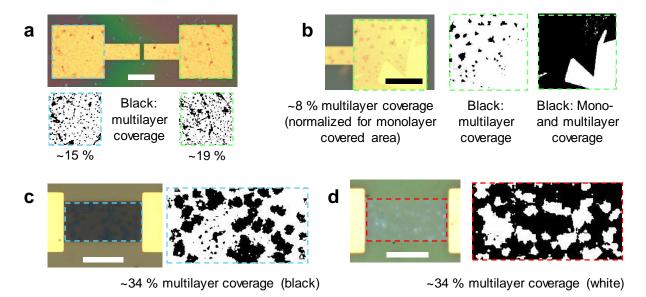

The amount of overgrowth and multilayers can vary depending on the location on the sample (edge vs. center) and between growths. This is further quantified by optical image analysis performed on samples used for flexible devices based on the transfer process described in this work. Supplementary Fig. 3a,b shows examples where unpatterned MoS<sub>2</sub> was transferred together with contacts (for *Type A* devices)

<sup>&</sup>lt;sup>1</sup>Department of Electrical Engineering, Stanford University, Stanford, CA 94305, U.S.A.

<sup>&</sup>lt;sup>2</sup>Geballe Laboratory for Advanced Materials, Stanford University, Stanford, CA 94305, U.S.A.

<sup>&</sup>lt;sup>3</sup>Department of Materials Science & Engineering, Stanford University, Stanford, CA 94305, U.S.A.

<sup>&</sup>lt;sup>†</sup>These two authors contributed equally. <sup>\*</sup>Corresponding author email: epop@stanford.edu

Supplementary Fig. 1 | Raman and photoluminescence (PL) mapping of an MoS<sub>2</sub> multilayer island surrounded by monolayer MoS<sub>2</sub> on SiO<sub>2</sub>/Si. a, Optical image of mapped area. b, PL peak height. c, PL peak position. d, Raman E' peak height. e, Raman E' peak position. f, Raman A<sub>1</sub>' peak height. g, Raman A<sub>1</sub>' peak position.

from the center of the chip (a) and from the chip edge (b). The threshold brightness analysis of these images indicates a multilayer coverage of 8-19%. For another example of *Type B* devices during processing (located in chip center), we find that the multilayer coverage can be as high as 34 %

Supplementary Fig. 2 | Raman and photoluminescence (PL) mapping of an MoS<sub>2</sub> grain boundary surrounded by monolayer MoS<sub>2</sub> on SiO<sub>2</sub>/Si. a, Optical image of mapped area. b, PL peak height. c, PL peak position. d, Raman E' peak height. e, Raman E' peak position. f, Raman A<sub>1</sub>' peak height. g, Raman A<sub>1</sub>' peak position.

Supplementary Fig. 3 | Optical analysis of mono- vs. multilayer regions of MoS<sub>2</sub>. a, Continuous MoS<sub>2</sub> film in chip center of a *Type A* device after transfer, scale bar: 50  $\mu$ m. b, Non-continuous MoS<sub>2</sub> region in chip edge of a *Type A* device after transfer, scale bar: 50  $\mu$ m. c, Etched MoS<sub>2</sub> film of a *Type B* device before transfer, scale bar: 20  $\mu$ m. d, Etched MoS<sub>2</sub> film of a *Type B* device after transfer, scale bar: 20  $\mu$ m.

(Supplementary Fig. 3c,d). Thus, for micron-scale devices we can assume that the channel will be mostly composed of monolayer MoS<sub>2</sub> (including multilayer islands), while most nanoscale channels will likely be monolayers with the occasional chance of continuous bilayers in the channel gap.

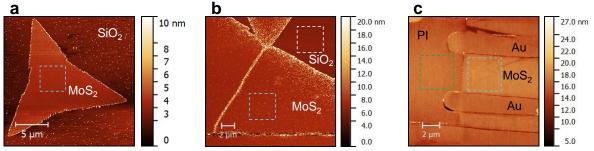

#### 2. Surface analysis before and after transfer

To investigate the surface morphology of the MoS<sub>2</sub> covered regions before and after transfer, we performed atomic force microcopy (AFM). We find that the as-grown MoS<sub>2</sub> has a root-mean-square (rms) roughness of 0.18 – 0.45 nm depending on growth run and sample location, which is comparable to or slightly larger than the nominal SiO<sub>2</sub> roughness (Supplementary Fig. 4). In addition, we have also measured the roughness after transfer and capping with 35 nm Al<sub>2</sub>O<sub>3</sub> (evaporated Al seed layer + atomic-layer deposition as described in Methods), which yielded a roughness of 0.39 nm on the MoS<sub>2</sub> covered region and 0.44 nm where MoS<sub>2</sub> was etched prior to transfer. This confirms that the extremely smooth MoS<sub>2</sub> surface is preserved even after transfer. In addition, the AFM reveals that the height difference between MoS<sub>2</sub> and Au surfaces is less than 2 nm which confirms that the 45 nm thick contacts are embedded in the substrate and topography is effectively eliminated. This is further visualized in the cross-section SEM image after completed device fabrication in Supplementary Fig. 5, where Al<sub>2</sub>O<sub>3</sub> and Au cover the contacts and channel without any "steps" in surface topography.

Note: Al<sub>2</sub>O<sub>3</sub> capped across the entire area.

**Supplementary Fig. 4** | **Atomic Force Microscopy** (**AFM**) of **a**, a single MoS<sub>2</sub> triangle on SiO<sub>2</sub>/Si with a root mean square (rms) roughness of 0.18 nm measured in region of light blue dashed box, **b**, an MoS<sub>2</sub> on SiO<sub>2</sub>/Si region of coalescing grains with rms roughness of 0.45 nm for MoS<sub>2</sub> (light blue dashed box) and 0.23 nm for the bare SiO<sub>2</sub> surface (white dashed box), and **c**, the MoS<sub>2</sub> and Au structures on polyimide after transfer and alumina capping (on the entire area) with rms roughness of 0.39 nm on the region with MoS<sub>2</sub> (light blue dashed box) and of 0.44 nm on the region where MoS<sub>2</sub> was etched (green dashed box).

**Supplementary Fig. 5** | Scanning-electron microscopy (SEM) cross-section of a ~100 nm long channel MoS<sub>2</sub> transistor, colorized version of Fig. 3a. Red dashed lines show the source and drain electrodes are embedded in the PI, and no "steps" in surface topography can be discerned.

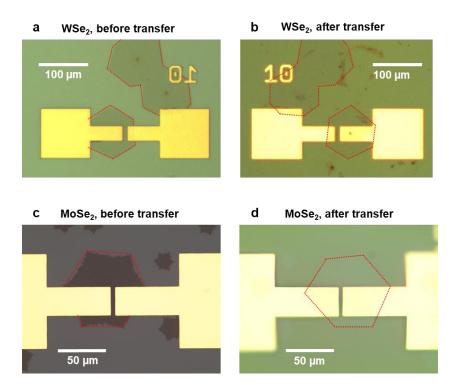

#### 3. Optical microscope images for WSe<sub>2</sub> and MoSe<sub>2</sub> before and after the transfer process

Supplementary Fig. 6a,c displays the hexagonally shaped WSe<sub>2</sub> and MoSe<sub>2</sub> crystal grains grown on SiO<sub>2</sub>/Si substrates after the patterning of source/drain metal contacts, and *before* the transfer. As visible here, the Au contacts are on top of the TMDs. When the polyimide (PI) is applied on top, it uniformly covers and embeds the contacts. After releasing the PI together with metals and TMDs from the SiO<sub>2</sub>/Si substrates (main text Fig. 1b), the substrate is flipped over as visible in the numbering ("10") when comparing Supplementary Fig. 6a,b. This also leads to a reversal of the material stack, where the TMDs are on top of Au/PI or PI, as visible in Supplementary Fig. 6b,d.

#### 4. Raman spectroscopy and Photoluminescence measurements before and after transfer process

The different TMDs were monitored with Raman spectroscopy and photoluminescence (PL) throughout the transfer process to investigate any changes in material properties. Supplementary

Supplementary Fig. 6 | Microscope images of WSe<sub>2</sub> and MoSe<sub>2</sub> with patterned Au metal electrodes. a, WSe<sub>2</sub> on SiO<sub>2</sub>/Si before transfer. b, WSe<sub>2</sub> on polyimide (PI) after transfer. c, MoSe<sub>2</sub> on SiO<sub>2</sub>/Si before transfer. d, MoSe<sub>2</sub> on PI after transfer.

Fig. 7a-f display the spectra for MoS<sub>2</sub>, WSe<sub>2</sub> and MoSe<sub>2</sub> before and after transfer. Because we have deposited and patterned metal contacts before the transfer, released all materials together, and flipped the flexible PI substrate, we were able to measure the TMDs after transfer on the metal surface and on the PI surface.

We observed that the measurements directly on PI (without a metal in between the TMD and PI) have a broad background signal, which is absent on the SiO<sub>2</sub>/Si substrates and on Au surfaces. This background signal is in the range where we expect the vibrational modes of the TMDs, and there is, for instance, a significant overlap with the PL energy maximum of monolayer MoS<sub>2</sub> (Supplementary Fig. 7b). The Raman and PL measurements for bare PI (on Si) are shown in Supplementary Fig. 7g,h for comparison. Because of this background signal, the MoS<sub>2</sub> Raman and PL peaks are buried and not visible in our measurements on PI. However, the peaks of WSe<sub>2</sub> and MoSe<sub>2</sub> on the PI surface can be resolved (Supplementary Fig. 7c-f). We note that a Raman laser with shorter wavelength could possibly help to reduce the background signal from PI and improve detection of TMDs.<sup>60</sup> Further, the insertion of Au between PI and the TMD suppresses this background signal and enables the detection of the Raman signature of all three TMDs.

Supplementary Fig. 7 | Raman (left column) and photoluminescence (right column) spectra. a,b, MoS<sub>2</sub>. c,d, WSe<sub>2</sub>. e,f, MoSe<sub>2</sub>. g,h bare polyimide (PI) on silicon.

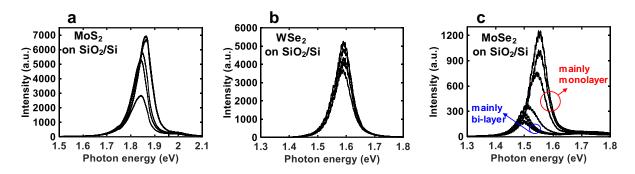

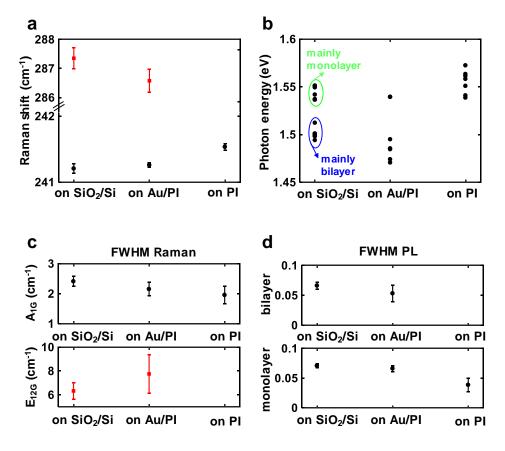

We find that the PL peaks for WSe<sub>2</sub> and MoSe<sub>2</sub> can be detected on PI and Au/PI despite the strong PL quenching that is known to appear on Au surfaces.<sup>33,34</sup> The PL peak energies of MoS<sub>2</sub>, WSe<sub>2</sub> and MoSe<sub>2</sub> are ~1.86 eV, ~1.59 eV and ~1.54 eV, all indicating monolayer thickness.<sup>29,61-63</sup> While these results were consistent for MoS<sub>2</sub> and WSe<sub>2</sub> across the substrate, we found that MoSe<sub>2</sub> had areas with monolayers and bilayers (~50%) (Supplementary Fig. 8), where the PL peak is shifted towards ~1.50 eV and its intensity is significantly reduced. The noticeable spread in PL energies for MoS<sub>2</sub> can be attributed to a variety of effects such as nanoscale bilayer regions<sup>27,28</sup> or small local variations in strain or doping. For MoSe<sub>2</sub>, however, we find two sets of PL energy peak positions, which indicate that some areas mainly consist of monolayers and some mainly of bilayers (~50% each).<sup>29,61</sup>

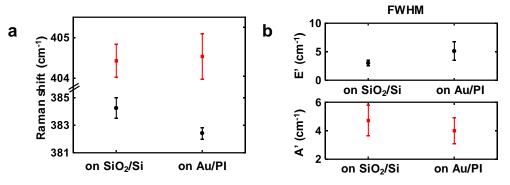

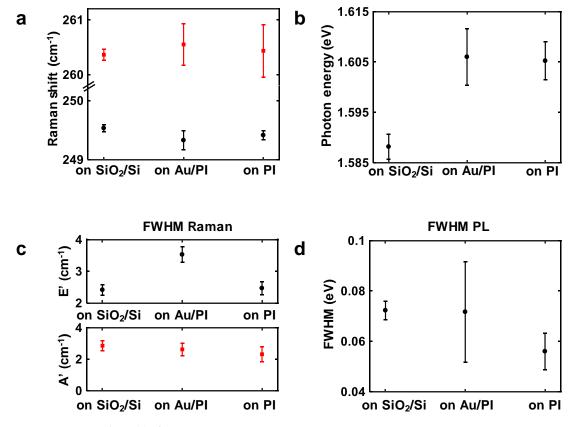

Changes in the Raman and PL spectra before vs. after transfer can be interpreted as strain release effects or phonon interactions with the bottom surfaces (PI or Au), as will be discussed in the following. For MoS<sub>2</sub> on Au, we find that the E' peak shifts by about -1.8 cm<sup>-1</sup> and its full-width-half-maximum (FWHM) increases, whereas the A'<sub>1</sub> peak does not change discernably (see Supplementary Fig. 9), which has been observed for non-transferred Au/MoS<sub>2</sub> stacks and thus cannot be correlated with the transfer process. Possible mechanisms for this E' peak shift and broadening can be tensile strain induced from the Au deposition<sup>64,65</sup> or electron-phonon interactions due to Au plasmons.<sup>66,67</sup> For WSe<sub>2</sub>, the changes in the Raman and PL spectra are small (Supplementary Fig. 10). The minor shifts in the PL peak position and Raman E' peak of about +0.02 eV and -0.1 to -0.2 cm<sup>-1</sup>, respectively cannot be consistently correlated with any strain release during transfer,<sup>68</sup> and may be related to small effects from interactions with the substrate.<sup>69</sup> It is difficult to deduce any strain effects from PL and Raman for MoSe<sub>2</sub>, due to small changes and existence of mono- and bilayers adding uncertainty to the Raman and PL analysis. Still, the results suggest the possibility of slight strain changes in tensile and compressive directions on Au/PI and PI surfaces, respectively (see Supplementary Fig. 11).<sup>70-72</sup>

**Supplementary Fig. 8** | PL measurements before transfer of **a**, MoS<sub>2</sub>, **b**, WSe<sub>2</sub> and **c**, MoSe<sub>2</sub>.

Overall, the FWHM of the Raman and PL peaks for all the TMDs do not increase except on Au electrodes, where previously discussed plasmonic effects could be the leading cause. This indicates that the disorder, which would be affected by crystal grain size or defect density, in the materials is not increased throughout the transfer process.<sup>73,74</sup> This conclusion is also supported by the good electrical

**Supplementary Fig. 9** | Averaged Raman (over ~5 spots on the same chip) **a**, peak positions and **b**, Full-width-half-maximum (FWHM) of MoS<sub>2</sub> before transfer (as-grown, on SiO<sub>2</sub>/Si substrate) and after transfer (on Au/PI).

**Supplementary Fig. 10** | Averaged (over ~5 spots on the same chip) **a**, Raman and **b**, photoluminescence (PL) peak positions of WSe<sub>2</sub> before and after transfer. Averaged full-width-half-maximum (FWHM) for **c**, the Raman and **d**, the PL measurements.

**Supplementary Fig. 11** | **a**, Averaged Raman (over  $\sim$ 5 spots on the same chip) and **b**, photoluminescence (PL) peak positions of MoSe<sub>2</sub> before and after transfer. Averaged full-width-half-maximum (FWHM) for **c**, the Raman and **d**, the PL measurements ( $\sim$ 10 spots across two chips). Note, missing data e.g., for the Raman E<sub>12G</sub> peak on PI means that these peaks could not be detected on that particular surface.

properties, which are comparable on the materials after transfer with those before transfer (i.e. on rigid SiO<sub>2</sub>/Si substrates) from previous studies using the same CVD material type.<sup>27,28,35</sup>

#### 5. Mobility, Gate Capacitance, and Threshold Voltage Extraction

We performed the extraction of the extrinsic field-effect mobility  $\mu_{\text{FE,ext}}$  and threshold voltage  $V_{\text{T}}$  from the  $g_{\text{m}}$  maximum based on the following equation (valid for small drain-source voltages  $V_{\text{DS}}$ ):

$$g_m = \frac{\partial I_D}{\partial V_{GS}} = \frac{\mu_{FE,ext}C_{ox}V_{DS}W}{L},$$

where the  $I_D$  plotted vs.  $V_{GS}$  can be fitted linearly to obtain  $\mu_{FE,ext}$ . Furthermore, the intercept with the  $V_{GS}$  axis yields  $V_T$ . The channel width W and the channel length L are given by the device geometry. The gate oxide capacitance per unit area ( $C_{ox}$ ) is determined by connecting source and drain of the

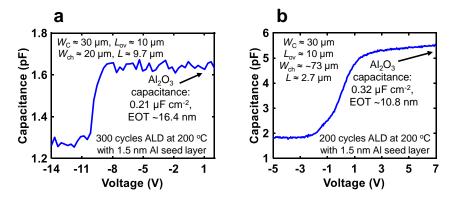

Supplementary Fig. 12 | Measured capacitance-voltage (C-V) characteristics of flexible TMD-FETs. Typical C-V for a, MoS<sub>2</sub> FETs and b, MoSe<sub>2</sub> and WSe<sub>2</sub> FETs, where the calculated Al<sub>2</sub>O<sub>3</sub> capacitance density and equivalent oxide thickness (EOT) represent average values ( $\sim$ 5 devices).  $L_{ov}$  is the overlap length between the gate electrode and the source/drain electrodes.

transistors to ground, and applying a voltage to the gate electrode. We then perform small-signal capacitance-voltage (C-V) measurements where the direct-current (dc) voltage is swept while applying an alternating-current (ac) voltage with an amplitude = 100 mV and frequency = 20 kHz. The results for Al<sub>2</sub>O<sub>3</sub> gate dielectrics (including 1.5 nm Al seed layer) deposited in 300 cycles (MoS<sub>2</sub> FETs) and 200 cycles (WSe<sub>2</sub> and MoSe<sub>2</sub> FETs) are shown in Supplementary Fig. 12a and b, respectively.

As all transistors are n-channel devices, we estimate the capacitance of the Al<sub>2</sub>O<sub>3</sub> gate dielectrics at positive bias voltage (when the channel is in accumulation) by dividing the measured capacitance (Supplementary Fig. 12) with the overlap area of the gate with the source, drain, and semiconductor channel.<sup>36</sup> For MoS<sub>2</sub> FETs the extracted  $C_{ox} \approx 0.21 \,\mu\text{F cm}^{-2}$  or an equivalent oxide thickness (EOT) ~16.4 nm, and for WSe<sub>2</sub> and MoSe<sub>2</sub> FETs we obtain  $C_{ox} \approx 0.32 \,\mu\text{F cm}^{-2}$  or EOT ~ 10.8 nm. Estimating the relative dielectric constant  $\varepsilon_{r}$  from  $C_{ox}$  and the Al<sub>2</sub>O<sub>3</sub> thickness obtained by ellipsometry, we find  $\varepsilon_{r} \approx 7$ -8, which is in the expected range.<sup>77,78</sup> Note, the ellipsometric thickness of 200 cycles and 300 cycles of atomic-layer deposited (200°C) Al<sub>2</sub>O<sub>3</sub> measured on silicon is around 22 nm and 35 nm, respectively. However, for the transistor capacitance the 1.5 nm oxidized Al seed layer adds to the overall thickness, while the optical lithography and lift-off process of the top (gate) electrode exposes the Al<sub>2</sub>O<sub>3</sub> to the basic photoresist developer which can etch the material, thus slightly reducing its thickness.

#### 6. Flexible MoS<sub>2</sub> Field-Effect Transistors of Type A

Supplementary Fig. 13 displays a top-down optical microscope image and the electrical characteristics of a flexible MoS<sub>2</sub> field-effect transistor (FET) of *Type A* with 4.7  $\mu$ m channel length. The device exhibits an extrinsic field-effect mobility  $\mu_{FE,ext} \sim 14.2 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ , on-current  $I_D \sim 5.5 \mu \text{A} \mu \text{m}^{-1}$  at a drain-

Supplementary Fig. 13 |  $MoS_2$  field-effect transistors (FETs) of *Type A*. a, Top-down optical microscope image, white dotted line marks the outline of the  $MoS_2$  area. b, Measured transfer characteristics. Red and blue lines represent drain current,  $I_D$ . c, Output characteristics.

source voltage  $V_{\rm DS} = 1$  V, threshold voltage  $V_{\rm T} = 3.9$  V, minimum subthreshold swing SS  $\approx 1.7$  V dec<sup>-1</sup> and on/off ratio  $\sim 3.6 \times 10^3$ . Note that  $\mu_{\rm FE,ext}$  and  $I_{\rm D}$  have been corrected for current spreading, which is described in Section 15 below.

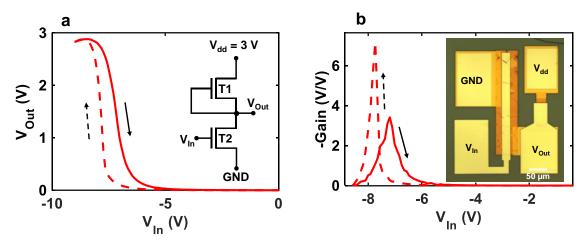

#### 7. Flexible $MoS_2$ Inverter based on Type B device fabrication process

The fabrication process for  $Type\ B$  devices further facilitates the realization of circuits because  $MoS_2$  is already defined before gate dielectric deposition and the second metallization, which simplifies connecting bottom and top metallization layers. For instance, these are useful for practical circuits, where the gates and source/drain contacts of some transistors need to be connected (see inset of Supplementary Fig. 14a). Supplementary Fig. 14 shows the characteristics of a proof-of-concept flexible inverter realized with two n-type  $MoS_2$  transistors.

Supplementary Fig. 14 | Flexible inverter with *Type B* MoS<sub>2</sub> transistors. a, Transfer characteristic of the inverter. Inset shows the schematic circuit diagram with transistors T1 ( $W_{ch}/L \approx 20/39.7 \,\mu$ m) and T2 ( $W_{ch}/L \approx 300/4.7 \,\mu$ m) b, Gain of the inverter shown in a. Inset shows an optical microscope image of the inverter after fabrication.

**Supplementary Fig. 15** | **Hysteresis in flexible transition metal dichalcogenide field-effect transistors. a**, MoS<sub>2</sub> (*Type A*). **b**, MoS<sub>2</sub> (*Type B*). **c**, WSe<sub>2</sub> (*Type A*). **d**, MoSe<sub>2</sub> (*Type A*).

#### 8. Hysteresis

Comparing hysteresis<sup>37</sup> for *Type A* and *Type B* devices, we find similar maximum values of  $\sim$ 1.2 V for MoS<sub>2</sub> FETs, which indicates that the additional etch step before transfer does not deteriorate the TMD interfaces (Supplementary Fig. 15a,b). The WSe<sub>2</sub> FET displays low hysteresis  $\sim$ 0.1 V (Supplementary Fig. 15c), and the MoSe<sub>2</sub> FET has maximum hysteresis of  $\sim$ 1.6 V (Supplementary Fig. 15d).

#### 9. Bending of flexible TMD FETs

Flexible electronics need to remain unaltered when mechanically deformed, for instance, by bending the substrate. While the ductility of materials matter for the maximum strain that flexible electronics can sustain,<sup>79</sup> the easiest way to minimize impacts of strain on flexible electronic devices is to minimize the substrate thickness. The strain at a given bending radius can be approximated as:<sup>80</sup>

$$strain = \frac{d}{2r}$$

**Supplementary Fig. 16** | **Mechanical bending of flexible TMD-FETs. a**, Photograph and microscope image (scale bar:  $200 \,\mu\text{m}$ ) of the measurement setup where the FETs are bent to a tensile radius of 4 mm. Measured transfer characteristics of **b**, WSe<sub>2</sub> (*Type A*), **c**, MoSe<sub>2</sub> (*Type A*) and **d**, MoS<sub>2</sub> (*Type A*). All show no significant changes on substrate bending at the 4 mm radius.

where d is the substrate thickness and r is the radius of curvature. Thus, by minimizing d to a few micrometers, the strain at common bending radii on the order of millimeters is minimized. We show this by using a ~5  $\mu$ m thick PI substrate and bending it to a radius of 4 mm, which results in ~0.063% of strain. Consequently, the electrical characteristics of the TMD FETs remain visually unaltered in this condition as shown in Supplementary Fig. 16.

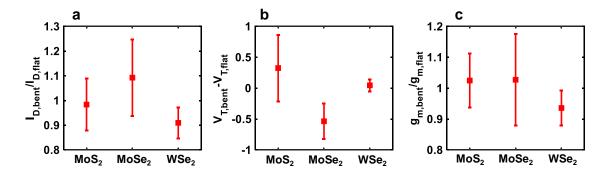

For a detailed quantitative evaluation, we have further analyzed transistor parameters such as drain current  $I_D$ , threshold voltage  $V_T$  and transconductance  $g_m$  (see Supplementary Fig. 17). Average  $I_D$  and  $g_m$  changes remain within 10% of the flat state values and absolute  $V_T$  shifts are mostly < 0.5 V. Given that the applied strain is low even at r = 4 mm, we conclude that no systematic correlations of strain with device performance parameters can be deduced from these results and we successfully confirmed the bending stability of our devices.

Supplementary Fig. 17 | Quantitative analysis of TMD transistors under bending to a radius of 4 mm. For MoS<sub>2</sub>, MoSe<sub>2</sub> and WSe<sub>2</sub>, displayed values represent the average and standard deviation of 12, 6 and 3 devices, respectively. a, Maximum drain current  $I_D$  under bending normalized by its value in flat condition. b, Threshold voltage shift  $V_{T,bent} - V_{T,flat}$ . c, Maximum transconductance  $g_m$  normalized by its value in flat condition.

#### 10. SEM images of transistor channels fabricated with electron-beam lithography (EBL)

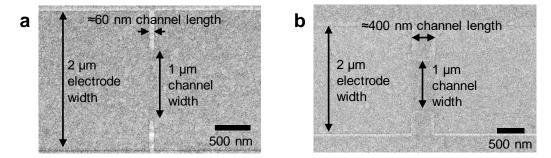

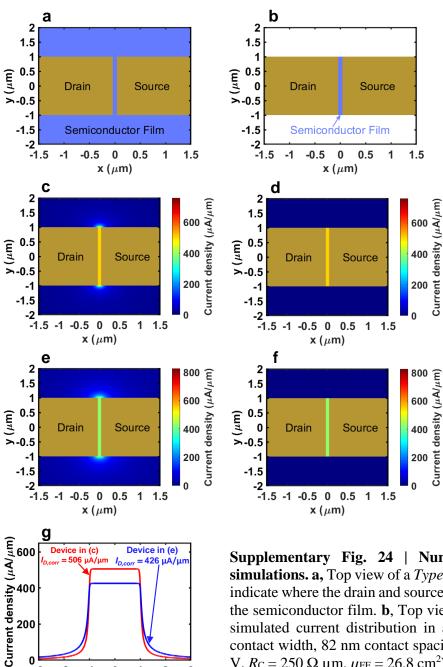

We verified the channel dimensions in our transistors by performing scanning-electron microscopy (SEM), which reveals the channel lengths and widths even after the top gate metal is deposited. Supplementary Fig. 18 shows two exemplary *Type B* devices with channel lengths of ~60 nm and ~400 nm. Note that the surface consists of Au across the whole area displayed since everything is covered with the top gate. Nevertheless it is possible to discern the edges where the MoS<sub>2</sub> has been etched. The MoS<sub>2</sub> etch mask consists of 2 µm wide metal leads (left and right) and photoresist covering the 1 µm wide channel region, which results in no discernable edge across the MoS<sub>2</sub> on Au and the MoS<sub>2</sub> in the channel. This is consistent with the absence of "steps" in surface topography from the SEM cross-sections (Supplementary Fig. 5) and AFM images (Supplementary Fig. 4). In our EBL process, the intended channel length was 50 nm, and after evaluating Supplementary Fig. 18a, we

**Supplementary Fig. 18** | **SEM top-view images of** *Type B* **transistors. a**, Device with a channel length ~60 nm. **b**, Device with a channel length ~400 nm.

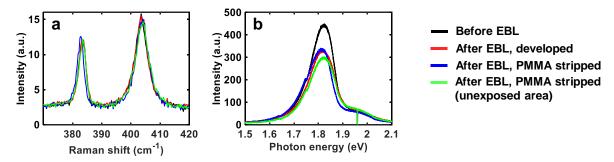

Supplementary Fig. 19 | Optical material analysis of MoS<sub>2</sub> throughout an electron-beam lithography (EBL) process involving spin-coating and stripping of poly(methyl methacrylate) (PMMA). a, Raman spectra. b, Photoluminescence spectra.

estimate its actual length is  $63 \pm 7$  nm. Analyzing 9 devices with sub-micron channels we find that on average the channel length is ~12 nm longer than intended in our device layout. Thus, we have corrected our extractions and evaluations on devices fabricated by EBL by  $\Delta L = +12$  nm. Similarly, we applied  $\Delta L = -0.3$  µm for devices fabricated by optical lithography based on SEM measurements.

#### 11. Electron Beam Lithography on top of MoS<sub>2</sub>

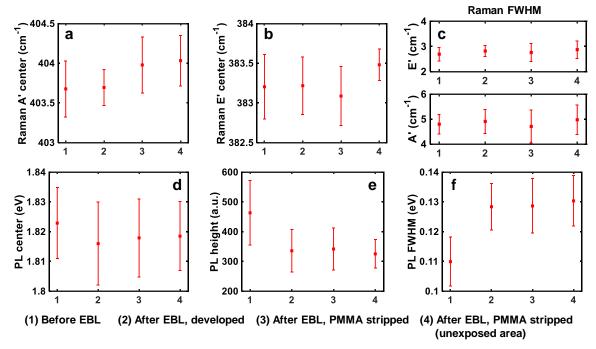

Previous reports have indicated that MoS<sub>2</sub> could be damaged by highly energetic electron beams which cause strain and defect formation. 81-84 We investigated this for our EBL process (details in the Methods section) performing Raman and PL measurements before and after the electron beam exposure and development of the poly(methyl methacrylate) (PMMA) layer that was used for the lift-off of the later deposited source/drain metal. Supplementary Fig. 19 displays exemplary Raman and PL spectra, while Supplementary Fig. 20 provides the analysis of Raman and PL peak center shifts as well as the changes in the intensity and FWHM of the PL spectra. We found negligible differences in the Raman spectra. The slight reduction in the PL intensity (Supplementary Fig. 19b) occurs independently of the exposure to the electron beam, and may be caused by PMMA residues or minor effects from processing and aging of the material. Thus, we conclude that here we do not cause significant damage during the EBL process, which may have been due to our 200 nm thick high molecular weight (950K) PMMA layer on top that should reduce the impact energy and dosage of electrons that hit the MoS<sub>2</sub>. The other parameters of our EBL process and the device fabrication can be found in the Methods section.

Supplementary Fig. 20 | Averaged optical material analysis of MoS<sub>2</sub> during electron-beam lithography (EBL) with spin-coating and stripping of poly(methyl methacrylate) (PMMA). a, Raman A' peak center. b, Raman E' peak center. c, Averaged full-width-half-maximum (FWHM) of the Raman peaks. d, Photoluminescence (PL) peak center. e, PL peak height. f, PL FWHM.

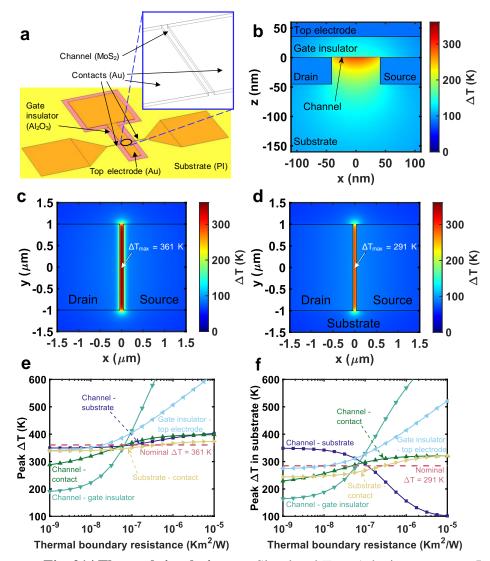

#### 12. Temperature Rise Estimates

We estimate the MoS<sub>2</sub> and PI substrate temperature rises in a short-channel ( $L \sim 82$  nm,  $W_C = 2$  µm)  $Type~A~MoS_2$  device. This particular "hero" device was chosen because it achieved the highest power dissipation, and is therefore expected to reach the highest temperatures during device operation. The operating point simulated is  $V_{GS} = 16~V$ ,  $V_{DS} = 1.2~V$  and  $I_D = 1.225~mA$ , which corresponds to the highest power (1.47 mW) demonstrated in Fig. 3f. In order to account for interface thermal resistances and various heat paths and current spreading, we perform 3D steady-state thermal finite element method (FEM) simulations, with the device geometry shown in Supplementary Fig. 21a. The 5 µm thick PI substrate is attached to a heat sink at  $T_0 \approx 20$ °C via photoresist (SPR 3612, Shipley), which serves as the thermal interface material. For simulations, a thermal contact resistance of 0.1 K·cm²/W was assumed at the bottom of the PI substrate (typical of contact resistances in device packaging shiple the exact value has little effect on simulated peak temperatures in this case, because its contribution to the total thermal resistance is much less than the thermal resistance of the PI substrate and the device thermal circuit. The thermal conductivities of the materials used in the simulations and the thermal boundary resistances (TBR) of material pairs are given in Supplementary Table 1.

| Material                                            | Thermal conductivity (Wm <sup>-1</sup> K <sup>-1</sup> ) | Material interface                         | Thermal<br>boundary<br>resistance<br>(Km²/GW) |

|-----------------------------------------------------|----------------------------------------------------------|--------------------------------------------|-----------------------------------------------|

| $MoS_2$ <sup>86</sup>                               | 20 (in-plane)                                            | MoS <sub>2</sub> – polyimide <sup>87</sup> | 100                                           |

| Polyimide (PI) <sup>88</sup>                        | 0.2                                                      | $MoS_2 - Au^{89}$                          | 67                                            |

| $Au^{90}$                                           | 150                                                      | $MoS_2 - Al_2O_3^{89}$                     | 67                                            |

| ALD Al <sub>2</sub> O <sub>3</sub> <sup>91,92</sup> | 2.5                                                      | Au/Ti - ALD Al2O392-95                     | 20                                            |

|                                                     |                                                          | Au – polyimide <sup>96</sup>               | 400                                           |

**Supplementary Table 1:** Nominal values of material thermal properties in the simulations. Some thermal boundary resistance (TBR) values not available in literature were approximated by TBRs for pairs of similar and/or better-studied materials, using the larger estimates to model a worst-case scenario. Actual values can vary depending on the material/interface quality and deposition conditions. For Au, the thermal conductivity of films with comparable thickness (not bulk) is used. For PI and Al<sub>2</sub>O<sub>3</sub>, the thermal conductivities above room temperature (in the 100-200°C range) are used.