www.acsnano.org

# High Current Density in Monolayer MoS<sub>2</sub> Doped by AlO<sub>x</sub>

Connor J. McClellan, Eilam Yalon, Kirby K. H. Smithe, Saurabh V. Suryavanshi, and Eric Pop\*

Cite This: ACS Nano 2021, 15, 1587-1596

**ACCESS** I

Metrics & More

Article Recommendations

s Supporting Information

ABSTRACT: Semiconductors require stable doping for applications in transistors, optoelectronics, and thermoelectrics. However, this has been challenging for two-dimensional (2D) materials, where existing approaches are either incompatible with conventional semiconductor processing or introduce time-dependent, hysteretic behavior. Here we show that low-temperature (<200 °C) substoichiometric AlO<sub>x</sub> provides a stable *n*-doping layer for monolayer MoS<sub>2</sub>, compatible with circuit integration. This approach achieves carrier densities >2 ×  $10^{13}$  cm<sup>-2</sup>, sheet resistance as low as ~7 k $\Omega$ / $\square$ , and good

contact resistance ~480  $\Omega\mu$ m in transistors from monolayer MoS<sub>2</sub> grown by chemical vapor deposition. We also reach record current density of nearly 700  $\mu$ A/ $\mu$ m (>110 MA/cm²) along this three-atom-thick semiconductor while preserving transistor on/off current ratio >10<sup>6</sup>. The maximum current is ultimately limited by self-heating (SH) and could exceed 1 mA/ $\mu$ m with better device heat sinking. With their 0.1 nA/ $\mu$ m off-current, such doped MoS<sub>2</sub> devices approach several low-power transistor metrics required by the international technology roadmap.

**KEYWORDS:** 2D semiconductors, current density, doping, high-field, self-heating, MoS<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>

he success of modern electronics has relied on conventional silicon transistor scaling, enabling advancements in computing technology year after year for over five decades. Recent field-effect transistors (FETs) have used top-down fabrication to realize ultrathin silicon "fins" (i.e., FinFETs)<sup>1,2</sup> for improved control of leakage current and performance. However, these approaches have limitations imposed by process variation and the degradation of silicon mobility in ultrathin, approximately sub-4 nm layers.<sup>3,4</sup> The emergence of sub-1 nm thin monolayer 2D semiconductors could therefore extend transistor scaling, representing the ultimate limit of semiconductors, without an analogue among bulk materials like silicon. For example, monolayer 2D semiconductors like MoS<sub>2</sub> could enable sub-5 nm scale transistors<sup>5</sup> and, owing to their direct band gap, could also allow integration with optoelectronic devices.<sup>6</sup> Recent research has demonstrated the integration properties of monolayer 2D semiconductors, including three-dimensional (3D) monolithic systems and flexible electronics.

However, the atomic thinness of 2D semiconductors has raised questions about the ability to dope them and, consequently, about their ultimate performance in integrated circuits. While doping bulk materials like silicon is achieved with substitutional impurities, such an approach in a three-atom-thick material could significantly degrade the mobility. In addition, performance can be judged based not only on (low-

field) mobility but also on the maximum drive current  $I_{\rm on}$  because circuit delays are proportional to  $CV/I_{\rm on}$ , where C is the capacitance including parasitics and V is the voltage. To meet International Roadmap of Devices and Systems (IRDS)<sup>9</sup> specifications for low-power transistors, the on-state current must exceed  $I_{\rm on} > 480~\mu{\rm A}/\mu{\rm m}$ , while the off-state current must remain  $I_{\rm off} < 0.1~{\rm nA}/\mu{\rm m}$ , ideally within a narrow voltage swing (e.g., 0.5 to 1 V) for low-power operation.

Past studies of doping 2D materials have explored surface functionalization of acceptor  $^{10,11}$  or donor  $^{12}$  states, but a large degradation in transistor subthreshold swing (SS) was often observed due to induced trap states. Chemical charge-transfer doping was also proposed;  $^{13,14}$  however, such approaches face stability and integration issues. Instead, substoichiometric metal oxides (like  $\rm MoO_x$  for  $p\text{-type}^{15}$  and  $\rm AlO_x$  or  $\rm TiO_x$  for  $n\text{-type}^{16,17}$ ) have been used as stable doping layers of 2D materials, but doped devices typically experience a severe reduction in on/off current ratio ( $I_{\rm on}/I_{\rm off}$ ) and poor SS. Such challenges have ultimately prevented the achievement of 2D

Received: October 30, 2020 Accepted: December 28, 2020 Published: January 6, 2021

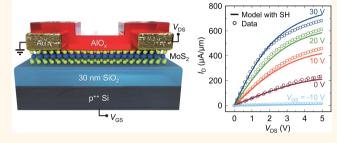

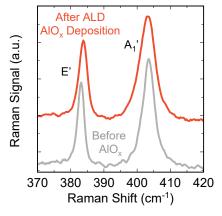

Figure 1. AlO<sub>x</sub> doped MoS<sub>2</sub> FET. (a) Schematic of FET with Au contacts, 16 nm AlO<sub>x</sub> capping, and monolayer MoS<sub>2</sub> channel grown on  $t_{\rm ox}$  = 30 nm SiO<sub>2</sub> with a highly doped Si substrate back-gate. (b) Atomic force microscopy (AFM) image of transfer length method (TLM) structures used for extracting contact and sheet resistances. (c) Photoluminescence (PL) measurements of MoS<sub>2</sub> before and after AlO<sub>x</sub> deposition and N<sub>2</sub> annealing, showing a decrease of intensity and slight red-shift in PL peak position after AlO<sub>x</sub> deposition. (d) Raman spectra of MoS<sub>2</sub> before and after AlO<sub>x</sub> deposition. The AlO<sub>x</sub> deposition induces a red-shift and asymmetry of the E' mode, consistent with the Fano effect of high doping,  $^{38,60,61}$  while the red-shift and peak broadening of the A<sub>1</sub>' mode has also been correlated with MoS<sub>2</sub> doping. The corresponding full-width half-maximums (FWHM) before AlO<sub>x</sub> are 3.2 cm<sup>-1</sup> (6.1 cm<sup>-1</sup>) for E' (A<sub>1</sub>') which then increase after AlO<sub>x</sub> deposition to 6.8 cm<sup>-1</sup> (7.3 cm<sup>-1</sup>) for E' (A<sub>1</sub>').

transistors with high on-current and good  $I_{\rm on}/I_{\rm off}$ . Furthermore, most doping studies on 2D semiconductors have been limited to thicker, multilayer semiconductors, <sup>13,18</sup> which have no clear technological benefit over ultrathin silicon-on-insulator (SOI) or FinFETs, <sup>1,19</sup> far more mature technologies.

In this work, we demonstrate a stable doping approach that preserves the transistor  $I_{\rm on}/I_{\rm off}$  while enabling record-high  $I_{\rm on}$ , record-low sheet resistance, and low contact resistance in a three-atom-thick semiconductor. These results are enabled by the increase in carrier concentration from doping while maintaining a low interface trap density through annealing. Importantly, this is achieved with MoS<sub>2</sub> grown by large-area chemical vapor deposition (CVD), which is necessary for practical applications. Our three-atom-thick MoS<sub>2</sub> transistors reach  $I_{\rm on}\approx 700~\mu{\rm A}/\mu{\rm m}$  at 5 V (~300  $\mu{\rm A}/\mu{\rm m}$  at 1 V) while maintaining  $I_{\rm off}<0.1~{\rm nA}/\mu{\rm m}$ . These achievements advance monolayer semiconductors to an important position for low-power logic and memory, approaching industrial specifications.

## **RESULTS AND DISCUSSION**

**Device Design.** Figure 1a shows the schematic of our transistors fabricated using monolayer  $MoS_2$  grown by CVD directly onto  $SiO_2$  ( $t_{ox} = 30$  nm) on highly doped ( $p^{++}$ ) Si, which also serves as a back-gate, with pure Au contacts (also see the Methods). The uncapped (and undoped) monolayer  $MoS_2$  has a field-effect mobility of 35 to 40 cm $^2$  V $^{-1}$  s $^{-1}$  in this work, which could range from 30 to 50 cm $^2$  V $^{-1}$  s $^{-1}$  in our previous studies on similar CVD-grown material. To dope these, we first use electron beam evaporation to deposit a thin 1 nm Al seed layer that immediately oxidizes upon air exposure to form substoichiometric  $AlO_x$ , followed by 15 nm of  $AlO_x$  deposited by atomic layer deposition (ALD), and additional details are given in the Methods. Figure 1b displays an atomic

force microscopy (AFM) image of multiple such  $MoS_2$  devices in a transfer length method (TLM) structure with channel lengths from L=180 to 980 nm, as measured. For good contact resistance ( $R_{\rm C}$ ) estimates, these TLM structures must include channel lengths ranging from "short" (dominated by their contacts) to "long" (dominated by the channel resistance).<sup>21</sup> Extrapolating  $R_{\rm C}$  only from long channel devices could lead to large uncertainty and even apparently negative contact resistance from TLM extractions.<sup>22</sup> The corresponding photoluminescence (PL) and Raman spectra before and after  $AlO_x$ -capping are displayed in Figure 1c,d, respectively, and additional details are provided in Supporting Section S1.

Doping vs Trapping Induced by the Oxide. Before presenting the electrical data, we note that doping the 2D material by metal oxides can result from at least two distinct processes. In the first process, the charge is induced by trap states at the semiconductor/oxide interface (classically referred to as  $D_{it}$ ) or in the oxide near the interface (e.g., border traps).23,24 These traps are energetically located within the energy gap of the 2D semiconductor and ultimately lead to degradation of mobility or SS. The other process for doping the 2D material is by transfer of electrons or holes from states that do not overlap with the energy gap of the 2D semiconductor, analogous to modulation doping in high electron mobility transistors (HEMTs).<sup>25</sup> Similar effects have been attributed to dipoles in high-k dielectrics on Si transistors, where dipoles affect the mobile carrier density in the channel.<sup>26</sup> In this case, the induced charge carriers end up in the conduction (valence) band for *n*-type (*p*-type) doping, and do not degrade the SS or mobility of the 2D transistor. Such techniques are commonly used in the semiconductor industry to adjust the threshold voltage  $(V_T)$  in Si transistors, utilizing either fixed charge or dipoles.2

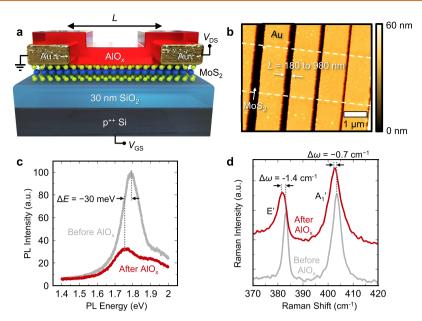

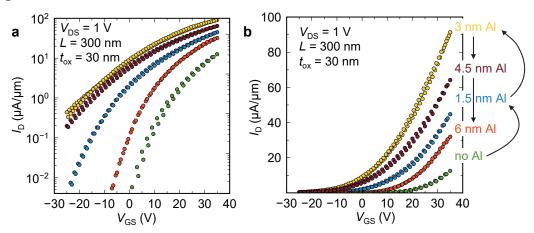

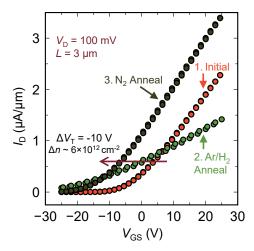

Figure 2. Trapping and doping in  $MoS_2$  FET. (a) Linear and (b) log scale measured transfer characteristics of  $MoS_2$  FET before  $AlO_x$  deposition (gray), after  $AlO_x$  deposition (light red), and after  $200\,^{\circ}C$   $N_2$  anneal for 40 min (dark red). The -12 V shift in  $V_T$  after  $N_2$  annealing indicates an induced negative charge density of  $\sim 8.6 \times 10^{12}$  cm $^{-2}$  in the  $MoS_2$ . Interface trap model fitting shown in (b) matches the experimental data, demonstrating how midgap trap states can pin the  $MoS_2$  Fermi level and reduce gate control. Small arrows show both backward and forward measurements (dual sweep), revealing minimal hysteresis. (c) Schematic band diagram of the trapping and doping states of the  $AlO_x/MoS_2$  interface,  $D^0$  being a defect with no charge,  $D^{1+}$  a defect with 1 positive charge, and  $D^{2+}$  a defect with 2 positive charges. Band bending in the  $AlO_x$  is shown schematically to illustrate presence of charge.

Figure 2a,b show measured linear and logarithmic drain current vs gate voltage of a 3 µm long MoS2 channel before AlO<sub>x</sub> deposition (gray), immediately after AlO<sub>x</sub> doping (light red), and after an anneal in N2 at 200 °C for 40 min (dark red). Note that all I-V measurements shown here include forward and backward sweeps, as labeled by small arrows, while the minimum and maximum gate voltages are limited by the breakdown field of the gate dielectric. Immediately after ALD of AlO<sub>x</sub> the carrier and current density increase, but the SS and transconductance  $(g_{\rm m} = \partial I_{\rm D}/\partial V_{\rm GS})$  degrade, indicating the as-deposited AlO<sub>x</sub> leads to carrier trapping. The induced trap density is high,  $\Delta D_{\rm it} \sim 5 \times 10^{13} \ {\rm cm}^{-2} \ {\rm eV}^{-1}$  estimated from the change in SS (Supporting Section S2). However, after annealing in  $N_2$  the SS, mobility, and  $g_m$  recover to their values measured in the undoped channel, with a negative  $V_T$  shift corresponding to  $\sim 8.6 \times 10^{12} \text{ cm}^{-2}$  electron doping (Supporting Section S3), and a current increase by >50% at the highest  $V_{GS}$  shown. The sheet resistance of this long channel after doping and annealing is the lowest reported for monolayer MoS<sub>2</sub> to date,  $R_{\rm sh} \approx 7~{\rm k}\Omega/{\rm \square}$  at room temperature, estimated after subtracting the small (<4%) contribution of the contact resistance discussed below.

The trapping and doping states observed in Figure 2a,b are linked to  $AlO_x$  defects and their energy distribution at or near the  $AlO_x/MoS_2$  interface.  $^{28-30}$  Figure 2c displays an energy band diagram of the doping effect, showing three defect states in  $AlO_x$  modeled previously using density functional theory (DFT),  $^{30}$  originating from oxygen vacancies in substochiometric  $AlO_x$ . These defect states each have a charge and energy level that depend on the electron occupation. Defects with high electron occupation have lower energy levels and no charge  $(D^0)$ , whereas removing electrons raises the defect energy level and leaves positive charge. The change in defect energy level from removing or adding electrons has been shown with DFT to occur from redistribution of the surrounding atoms in the metal oxide, changing the required energy to add or remove an electron, respectively.  $^{28-30}$

Shallow defects that have energy levels within the  $MoS_2$  band gap and available electron states ( $D^{1+}$ ) lead to trapping of  $MoS_2$  channel electrons, decreasing their mobility because the localized electrons "hop" between defects.<sup>31</sup> If the defects donate their electrons and reside at energy levels above the

${\rm MoS_2}$  conduction band  $({\rm D^{2+}})$ , the  ${\rm MoS_2}$  electrons are not trapped. These higher energy defect states donate electrons and become positively charged, inducing negative (mobile) charge in the  ${\rm MoS_2}$  channel. Remote Coulomb scattering with these charged  ${\rm D^{2+}}$  states could limit the channel mobility, as is the case for  ${\rm HEMTs}$ ,  $^{32}$  but this is not observed here as the  ${\rm MoS_2}$  mobility after  ${\rm AlO}_x$  capping and anneal is virtually unchanged from the uncapped samples. This indicates that such remote Coulomb scattering is either screened by the  ${\rm AlO}_x$  or that the  ${\rm MoS_2}$  mobility is more strongly limited by intrinsic defects and phonons in our samples.  $^{33}$

Using the Stanford 2D Semiconductor (S2DS) FET model, <sup>34</sup> we successfully simulate the data in Figure 2b. The model can describe both the subthreshold (diffusion) and above-threshold (drift) current components, with additional details in Supporting Section S3. The large degradation of SS immediately after AlO<sub>x</sub> deposition is due to midgap defects, included in the model as an interface capacitance ( $C_{\rm it} = q^2D_{\rm it}$ )<sup>27</sup> which reduces the overall gate capacitance ( $1/C_{\rm G} = 1/C_{\rm ox} + 1/C_{\rm it}$ ) where q is the elementary charge and  $C_{\rm ox} = \epsilon_{\rm ox}/t_{\rm ox}$   $\epsilon_{\rm ox}$  and  $t_{\rm ox}$  being the permittivity and thickness of the SiO<sub>2</sub>, respectively. Thus,  $C_{\rm G} < C_{\rm ox}$ , which can lead to an overestimation of carrier density and underestimation of mobility (Supporting Section S3).

The good agreement between the experimental data and the  $D_{\rm it}$  model shows how trapping and doping can be induced by changing the energy level and defects density in the  ${\rm AlO}_x$ . Annealing in a nonreactive, inert  ${\rm N}_2$  ambient  $^{35,36}$  after  ${\rm AlO}_x$  deposition helps promote the defects to donate electrons to the  ${\rm MoS}_2$ , analogous to dopant activation steps in conventional semiconductors. These results highlight the difference between trapping and doping of mobile charge in 2D materials. Here we achieve 2D doping without degradation of  $I_{\rm on}/I_{\rm off}$ , unlike previous studies where the decreased  $I_{\rm on}/I_{\rm off}$  was (incorrectly) attributed to large doping, although this was likely a  $D_{\rm it}$  effect.

We also fabricated long channel ( $L=6~\mu m$ ) top-gated MoS<sub>2</sub> FETs using the AlO<sub>x</sub> as the top gate insulator (Supporting Section S4). As expected, we found that after anneal (the doping state), the AlO<sub>x</sub> enables good electrostatic control and low gate leakage, evidence of an insulating oxide. However, before anneal (in the AlO<sub>x</sub> trapping state) the top gate control was weak and the gate leakage current was much higher (see

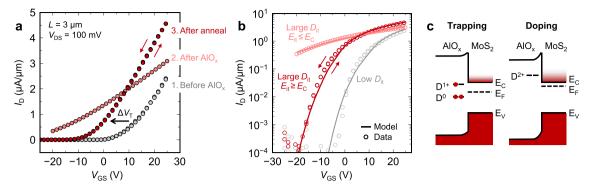

Figure 3. Electrical characteristics in trapping and doping states of MoS<sub>2</sub> FET. (a) Effective mobility ( $\mu_{\rm eff}$ ) and (b) contact resistance ( $R_{\rm C}$ ) extractions vs electron concentration with the TLM. The doping state (dark red) demonstrates higher  $\mu_{\rm eff}$  than the trapping state (light red), as the reduction in traps yields a lower sheet resistance of the MoS<sub>2</sub>. By reaching higher carrier density, our highly doped Au-1L MoS<sub>2</sub> FETs demonstrates lower  $R_{\rm C}$  than previously measured  $R_{\rm C}$  between Ag-1L MoS<sub>2</sub> and Au-7L MoS<sub>2</sub>. <sup>21,43</sup> (c) Measured output and (d) log-scale transfer characteristics of a 380 nm long AlO<sub>x</sub>-doped MoS<sub>2</sub> device, reaching nearly ~700  $\mu$ A/ $\mu$ m while maintaining a high on/off ratio of ~10<sup>6</sup>. The doping method is stable with only slight degradation after 60 days in air, as shown in (d). Every I-V shows forward and backward measurements (small arrows), with minimal hysteresis.

Supporting Section S4). The leaky  $AlO_x$  in the trapping state is consistent with defect states within the  $MoS_2$  band gap, which lead to trap-assisted tunneling and therefore gate leakage.

We have analyzed other substoichiometric oxides for doping 2D materials in previous studies, including  $MoO_3$  (for *p*-doping  $WSe_2$  and graphene),  $^{15,37}$  as well as  $TiO_x$  and  $NiO_x$ . However, we find that  $AlO_x$  provides the best results for *n*-type doping likely due to the Al seed not reacting with nor damaging  $MoS_2$ . In contrast, Ti and Ni can react with and damage monolayer  $MoS_2$ ,  $^{38}$  respectively, leading to lower mobility.

Contact and Sheet Resistance. To obtain the contact resistance of the doped MoS<sub>2</sub>, we use the TLM structures<sup>21</sup> shown in Figure 1b and measure resistance vs length (Figure S5). Figure 3a displays the effective mobility ( $\mu_{\text{eff}}$ ) here an average over the six channels) from the sheet resistance, before and after the N<sub>2</sub> anneal. The mobility increases from 12.8 cm<sup>2</sup>  $V^{-1}$  s<sup>-1</sup> before the anneal (due to the large  $D_{it}$ ) to 33.5 cm<sup>2</sup>  $V^{-1}$ s<sup>-1</sup> after the anneal, similar to that of our undoped monolayer  $MoS_2$ . The average sheet resistance is  $R_{\rm sh} = 9.0 \pm 0.5 \text{ k}\Omega/\Box$ at  $n \approx 2 \times 10^{13} \text{ cm}^{-2}$  in this TLM and  $\sim 7 \text{ k}\Omega/\Box$  in the doped long-channel device of Figure 2a. These are the lowest sheet resistances observed to date for monolayer MoS2 at room temperature, comparable to those achieved using superionic conductor (LaF<sub>3</sub>) gating at the lower temperature of 220 K.<sup>39</sup> Figure 3b shows the contact resistance vs n, reaching as low as  $R_{\rm C} \approx 480 \ \Omega \cdot \mu \rm m$  for Au with monolayer MoS<sub>2</sub> after AlO<sub>x</sub> doping. This is also the lowest contact resistance to any CVD-

grown monolayer semiconductor and one of the lowest among all 2D semiconductors.  $^{16,40}\,$

We attribute the low  $R_{\rm C}$  to the reduction in Schottky barrier width between Au and MoS<sub>2</sub> with increased carrier concentration, although the AlO<sub>x</sub> doping layer only touches the edge of the contact. This reduction in  $R_{\rm C}$  from channel doping has been observed before 15,16 and can be attributed to two causes. First, as the  $R_{\rm sh}$  of the metal is far less than that of the 2D material, the current transfer length ~50 nm (i.e., region of current injection under the contact, see Supporting Section S5), leading to most of the current being injected very close to the contact edge. 41,42 Second, due to the 2D nature of the channel, the depletion region of the Schottky contact extends beyond the contact edge into the channel.<sup>41</sup> As a result, increasing the carrier density by AlO<sub>x</sub> doping at or near the edge of the metal contact reduces the Schottky depletion region, increasing tunneling from metal to semiconductor as is observed in highly doped Si/metal contacts. This is further evidenced by comparing this result to our previous  $R_{\rm C}$  results in MoS<sub>2</sub> devices, <sup>21,43</sup> as shown in Figure 3b, where the new reduction in R<sub>C</sub> is achieved by reaching higher carrier densities through the use of  $AlO_x$  doping.

The low  $R_{\rm C}$  and  $R_{\rm sh}$  in our monolayer MoS<sub>2</sub> allow us to reach a maximum current  $I_{\rm on}\approx 690~\mu{\rm A}/\mu{\rm m}$  in a 380 nm long channel at  $V_{\rm DS}=5~{\rm V}$  (Figure 3c), achieving a record current density  $J_{\rm on}>110~{\rm MA/cm^2}$  for the three-atom-thick MoS<sub>2</sub> with  $t_{\rm ch}=6.15~{\rm Å.}^{44}$  This current density is the highest recorded to date in a 2D semiconductor, approximately 5× higher than the

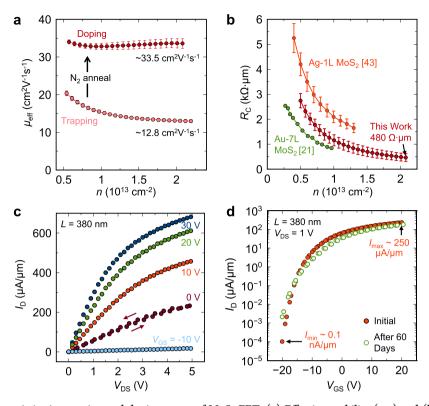

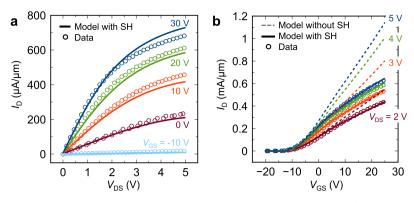

Figure 4. High current density and self-heating in  $AlO_x$ -doped  $MoS_2$  FET. Measured data (symbols) compared to model with self-heating (with SH, lines) and model without self-heating (without SH, dashed). The (a) output and (b) transfer characteristics correspond to the device in Figure 3, with L=380 nm. The model includes self-heating with measured thermal conductance. Including self-heating accurately reflects the saturation of current, while the model without self-heating suggests  $I_D$  could reach over 1 mA/ $\mu$ m. The simulations also capture the decrease of the saturation voltage  $(V_{Dsat})$  with increasing  $V_{GS}$ , which is only modeled correctly when including self-heating.

typical electromigration current densities of common metals and surpassed only by that of graphene (a 2D semimetal)<sup>45</sup> and carbon nanotubes<sup>46</sup> which are near ~1 GA/cm². Strictly speaking, this device reaches  $I_{\rm D}\approx 300~\mu{\rm A}/\mu{\rm m}$  at  $V_{\rm DS}=1~{\rm V}$  and the IRDS low-power specification<sup>9</sup> (>480  $\mu{\rm A}/\mu{\rm m}$ ) is met at  $V_{\rm DS}=2~{\rm V}$ . To meet this at  $\leq 1~{\rm V}$  would require a 2-fold improvement in mobility or a combined increase in mobility and carrier density, coupled with a reduction of contact resistance. We also keep in mind that the device shown in Figure 3c has L=380 nm, whereas the IRDS specifications<sup>9</sup> are meant for FETs of 10–20 nm channel length.

Figure 3d shows the transfer characteristics of the same transistor, demonstrating stable doping with only slight degradation after 60 days in air, and negligible hysteresis (both forward and backward measurement sweeps are shown). The device can turn off to 0.1 nA/ $\mu$ m and exhibits  $I_{\rm on}/I_{\rm off} \approx$  $2.5 \times 10^6$  at  $V_{\rm DS} = 1$  V despite the high doping (see Supporting Section S6 for  $V_{DS} = 2$  and 5 V) contrasting other doped 2D material transistors where the high on-state current was only achieved with low on/off ratio. These metrics are comparable to or better than those of recent silicon-on-insulator (SOI) devices, 47 yet achieved in a ~16 times thinner monolayer MoS<sub>2</sub> channel, and additional comparisons are provided in the Benchmarking section below. We emphasize that reaching high on-current density while preserving SS and sufficient  $I_{\rm on}/I_{\rm off}$  is a critical figure of merit to benchmark practical doping techniques of 2D materials.

**Current Density Limits.** Despite the record current density achieved here in a three-atom-thick semiconductor, it is important to ask what is limiting the maximum current and whether this could be improved further, given that high current (per transistor width) is required for high speed circuit operation. With a fixed parasitic resistance of 960  $\Omega \cdot \mu$ m (=  $2R_{\rm C}$ ) and channel resistance of 300  $\Omega \cdot \mu$ m, our devices could reach 600  $\mu$ A/ $\mu$ m at 20 nm gate lengths and  $V_{\rm DS}=0.75$  V, meeting IRDS low-power specifications. In comparison, state of the art Si or III–V transistors can reach >1 mA/ $\mu$ m,  $^{1,48}$  but in much "thicker" channels.

The maximum current density of a transistor is limited by mobility or saturation velocity, carrier density, contact resistance, and self-heating (SH) during operation. Naturally, higher mobility (such as in III-V semiconductors or graphene) automatically leads to higher current density, but high carrier density can compensate for a lower-mobility

semiconductor (as in this work). Shorter channel transistors can also reach higher operating currents, down to channel lengths that are limited by their contact resistance and injection velocity. However, with a "given" set of material and contact parameters, we find that self-heating ultimately limits the maximum current achieved in our devices.

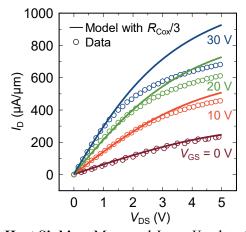

To understand this, we turn to Figure 4, which compares our measurements (symbols) with simulations (lines) including velocity saturation,  $^{43}$  contact resistance, and self-heating effects (further details provided in Supporting Section S7). By including these effects, our simulations capture the deviation from linearity in Figure 4a, at high drain bias  $V_{\rm DS} > 2$  V. These devices heat up significantly during measurement due to the high current density and relatively high thermal resistance of the MoS $_2/{\rm SiO}_2$  interface and the SiO $_2$  substrate.  $^{50}$  Thus, as the input power ( $\propto I_{\rm D}V_{\rm DS}$ ) increases, the temperature rise  $\Delta T$  degrades the electron mobility and saturation velocity. We estimate  $\Delta T \sim 400$  K channel temperature rise at the highest bias probed here, with heat flow being limited by the relatively low thermal boundary conductance between MoS $_2$  and SiO $_2$  (TBC  $\sim 15$  MW m $^{-2}$  K $^{-1}$ ).  $^{50}$

We also compare the measurements with our simulations in Figure 4b. The simulations including self-heating (solid lines) faithfully reproduce the experimental data, while simulations without self-heating (dashed lines) predict much higher current. The measured transconductance  $(g_m = \partial I_D/\partial V_{GS})$ decreases with increasing gate voltage  $V_{\rm GS}$ . In transistors based on typical bulk semiconductors (e.g., Si or III-Vs) such behavior is attributed to either contact resistance or mobility degradation from increased surface scattering at the higher transverse electric fields.<sup>27,51</sup> However, 2R<sub>C</sub> only accounts for ~26% of the total resistance even at  $n = 2 \times 10^{13}$  cm<sup>-2</sup> for this MoS<sub>2</sub> device, and we find no degradation of mobility with increasing  $V_{GS}$  (Figure 3a), as the electrons are already highly confined within the three-atom-thick semiconductor. The  $g_{\rm m}$ decrease is also more pronounced at higher  $V_{\rm DS}$ , i.e., higher input power, indicating that self-heating effects limit our MoS<sub>2</sub> transistor performance at high fields.

Simulations without self-heating (dashed lines in Figure 4b) reveal this transistor could reach  $I_{\rm on}\approx 1.2~{\rm mA/\mu m}$  at  $n\approx 2\times 10^{13}~{\rm cm^{-2}}$  and  $V_{\rm DS}=5$  V. These findings are consistent with recent studies of velocity saturation in monolayer MoS<sub>2</sub>,  $^{43,52}$  underlining that self-heating dominates the measured high-field behavior, and suggesting that other reports of high current in

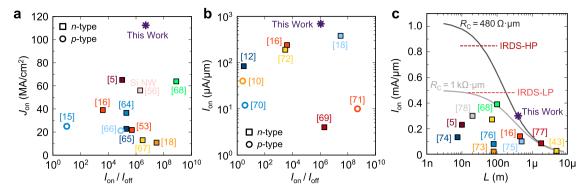

Figure 5. Benchmarking various 2D semiconductor FETs. (a) Maximum current density  $(J_{\rm on}=I_{\rm on}/t_{\rm ch})$  vs  $I_{\rm on}/I_{\rm off}$  for our monolayer MoS<sub>2</sub>, for other high-current 2D semiconductor devices  $^{5,15,16,18,53,64-68}$  of varying layer thickness (0.6 nm  $\leq t_{\rm ch} \leq 14$  nm), and a Si nanowire device.  $^{56}$  (b) Maximum  $I_{\rm on}$  vs  $I_{\rm on}/I_{\rm off}$  of our AlO<sub>x</sub>-doped MoS<sub>2</sub> compared with other doped 2D-FETs.  $^{10,12,16,18,69-72}$  While some doping methods yield high  $I_{\rm on}$ , the  $I_{\rm on}/I_{\rm off}$  can be much lower due to charge trapping in the 2D material or its interface. (c) Benchmarking of monolayer MoS<sub>2</sub> transistor  $I_{\rm on}$  vs channel length (L) at  $V_{\rm DS}=1$  V.  $^{5,16,43,68,73-78}$  Also shown are IRDS high-performance (HP) and low-power (LP) metrics at  $V_{\rm DS}=0.75$  V and 10-20 nm gate lengths. The simple model (solid lines) estimates achievable  $I_{\rm on}$  with  $R_{\rm C}=480$   $\Omega$ · $\mu$ m (this work) or 1 k $\Omega$ · $\mu$ m. The low  $R_{\rm C}$  achieved in this work (or lower) is needed to meet IRDS-HP metrics at reduced channel lengths. The data points are representative and not exhaustive. A more complete data set is available on our 2D transistor benchmarking website.  $^{58}$

2D transistors are also limited by self-heating.  $^{16,18,53}$  (Also see Supporting Section S7.) We note that even with thinner insulating substrates (here the SiO<sub>2</sub> is only 30 nm), thermal dissipation is limited by poor heat transfer across the weak van der Waals  $MoS_2/SiO_2$  interface, which is equivalent in thermal resistance to ~90 nm of  $SiO_2$ . Thus, future efforts must consider improving heat dissipation in 2D transistors or operating them in a transient regime that is faster than typical thermal time constants,  $^{52}$  which are sub-nanosecond for the 2D material  $^{54}$  and of the order 10-100 ns for the transistor including its gate and dielectrics.  $^{55}$

**Benchmarking.** Figure 5a compares our results with other reports of high current in 2D semiconductors (from monolayer to  $\sim$ 14 nm thick) and various doping studies, including a fully depleted Si nanowire FET. Here, we normalize the current by the conduction area  $[J_{\rm on}=I_{\rm on}/(Wt_{\rm ch})]$ , as opposed to only channel width to account for the channel thickness  $t_{\rm ch}$ , which is a key limiter in transistor scaling. Figure 5a reveals that while many 2D transistors display good on/off ratio, they lack the current density to compete with high-performance Si technology. By achieving high current drive in atomically thin, monolayer MoS<sub>2</sub> we surpass the current density of Si nanowires while maintaining good electrostatic control, highlighting the large current density and excellent electrostatics of 2D semiconductors.

These are the monolayer semiconductor transistors with the best current density reported to date, approaching IRDS low-power requirements both in terms of  $I_{\rm on}$  and  $I_{\rm off}$ . We also compare our results with other 2D material doping studies by plotting  $I_{\rm on}$  vs  $I_{\rm on}/I_{\rm off}$  in Figure 5b. As before, we emphasize that doping methods of 2D materials should not only be evaluated on the basis of  $R_{\rm sh}$ ,  $R_{\rm C}$ , and  $I_{\rm on}$ , but also on SS and  $I_{\rm on}/I_{\rm off}$ , as the inability to turn off 2D FETs could be an indication of charge traps. Figure 5b shows that most doping methods can induce high current in 2D semiconductors, but often by sacrificing  $I_{\rm on}/I_{\rm off}$ . As with our observations of trapping vs doping using AlO<sub>x</sub>, the doping methods that display low  $I_{\rm on}/I_{\rm off}$  could be introducing a substantial number of midgap traps. Furthermore, many of these methods have not been applied to 2D monolayers (as in this work), which are

electrostatically more favorable and represent the "ultimate atomic limit" of semiconductors.

Finally, in Figure 5c we compare the  $I_{on}$  achieved in this work and in previous studies of monolayer MoS2 as a function of transistor channel length, at the same  $V_{DS} = 1$  V and maximum  $V_{GS}$  reported. Solid curves are a simple model with  $I_{\rm D} = V_{\rm DS}/(LR_{\rm sh} + 2R_{\rm C})$  where  $R_{\rm sh} = (qn\mu)^{-1} \approx 8.1 \ {\rm k}\Omega/{\rm m}$  is the average channel sheet resistance with  $n = 2.2 \times 10^{13} \ {\rm cm}^{-2}$ ,  $\mu =$ 35 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, and  $R_C = 1 \text{ k}\Omega \cdot \mu \text{m}$  (achieved previously, 5,43 gray line) or 480  $\Omega \cdot \mu$ m (achieved in this work, black line). The horizontal red lines show the IRDS low-power (LP) and highperformance (HP) requirements (at a more aggressive 0.75 V in 10-20 nm gate length FETs). It is evident that micronscale devices are limited by their mobility, but short channels  $(L < 2R_C/R_{sh}$ , especially <100 nm) are strongly limited by their contacts. Thus, we expect that the largest improvements of short-channel MoS<sub>2</sub> transistors will be achieved by further reducing the contact resistance, together with reduction of equivalent oxide thickness (EOT) which will allow lowering V<sub>GS</sub>. More benchmarking data on multilayer and other 2D semiconductor transistors are summarized on a new website<sup>St</sup> recently launched while preparing this manuscript.

## **CONCLUSIONS**

We have demonstrated the doping effect of substoichiometric AlO<sub>x</sub> on monolayer CVD-grown MoS<sub>2</sub>. By activating dopants and reducing trap densities, we achieved record transistor current of nearly 700  $\mu$ A/ $\mu$ m at 5 V (~300  $\mu$ A/ $\mu$ m at 1 V), limited primarily by self-heating due to large current densities. The doping achieved with  $AlO_x$  is stable, also yielding excellent sheet resistance (down to 7 k $\Omega/\Box$ ) and contact resistance (down to 480  $\Omega \cdot \mu m$ ) for monolayer MoS<sub>2</sub> without degrading mobility or subthreshold swing. In contrast, previous 2D material doping methods often induced large density of interface traps that limit on- and off-state current. These interface traps can also lead to an overestimation of carrier density and underestimation of mobility. Future work should focus on selective doping near contacts, doping of the channel for threshold voltage control, p-type doping to enable CMOS and reducing the gate oxide thickness for lower gate voltages of high-performance transistors and 2D circuits.

## **METHODS**

MoS<sub>2</sub> FET Fabrication. Monolayer MoS<sub>2</sub> was deposited using a chemical vapor deposition  $(\text{CVD})^{20}$  process directly onto  $t_{ox} = 30 \text{ nm}$ of thermal dry  $SiO_2$  on  $p^{++}$  Si substrate (electrical resistivity of 1 to 5 mΩ·cm), which acts as a global back-gate. The MoS<sub>2</sub> was first etched into ~2 µm wide rectangular channels using electron beam lithography (EBL) and a XeF2 etch. Source and drain electrical contacts were defined using EBL with channel lengths varying between 180 nm and 3  $\mu$ m. EBL steps used 950 K poly(methyl methacrylate) (PMMA) for the resist, with either A5 PMMA for large features (i.e., pads, channel) or A2 PMMA for small features (i.e., contacts). For EBL writing, we used a Raith 150 operating at 20 kV acceleration voltages using doses of 180  $\mu$ C cm<sup>-2</sup> for A2 PMMA and 380  $\mu C$  cm<sup>-2</sup> for A5 PMMA. Pure Au contacts of 35 nm thickness were deposited on the MoS<sub>2</sub> using electron beam evaporation at highvacuum ( $\sim$ 8 × 10<sup>-8</sup> Torr) followed by lift-off in acetone and isopropyl alcohol cleaning.<sup>21</sup> We stress the importance of using pure Au contacts to MoS<sub>2</sub> for a clean contact interface, compared to metals that oxidize or react with the monolayer MoS2. Fabricating Au contacts without Ti or Cr adhesion layers requires careful processing, applying very little agitation to the sample during lift-off, and utilizing the pure Au only for the contacts and leads, not the large probing pads (which do have a ~3 nm Ti adhesion layer). The large probing pads (away from the device channels) were a stack of 20 nm SiO<sub>2</sub>, 3 nm Ti, and 40 nm Au, with the additional SiO<sub>2</sub> to limit leakage current from the 200  $\times$  200  $\mu$ m pad area to the substrate. If these steps are carefully followed, our liftoff yield is about 70% for the Au contacts vs the Ti/Au probing pads.

**Measurements.** All electrical measurements in this work were performed in the dark and under vacuum ( $<10^{-5}$  Torr) using a Keithley 4200-SCS parameter analyzer, in a Janis ST-100 probe station, at room temperature. We scratched through the  $AlO_x$  layer on top of the electrical pads using the W probe tip to make electrical contact with the Au. All plotted I-V data shows both forward and backward sweeps, indicating minimal hysteresis in our devices. For measuring the transistor on/off current ratio, we divide the maximum on current  $(I_{on})$  by the minimum off current  $(I_{off})$  over the whole gate voltage sweep. Raman and PL data were taken using a Horiba Labram with 532 nm excitation laser.

AlO<sub>x</sub> Deposition. For the AlO<sub>x</sub> capping and doping layer, an Al seed layer was first deposited on the MoS<sub>2</sub> devices by electron beam evaporation at a base pressure of  $\sim$ 4 × 10<sup>-7</sup> Torr. After exposure to air, the Al seed layer immediately oxidizes into AlO<sub>x</sub>. Supporting Section S8 shows the Al seed layer doping effect on MoS<sub>2</sub> FETs by applying several cycles of 1.5 nm Al deposition and oxidizing in air for 2 h. We use a 1 nm Al layer to seed  $\sim$ 15 nm of AlO<sub>x</sub> deposited by ALD at 150 °C with a trimethylaluminum precursor and H<sub>2</sub>O oxidizing step. The Al seed layer promotes the nucleation of ALD AlO<sub>x</sub> for complete coverage of the MoS<sub>2</sub>. <sup>59</sup> We also found that hydrogen annealing can effectively reduce the AlO<sub>x</sub>, increasing the trap density and doping (Supporting Section S9).

## **ASSOCIATED CONTENT**

## Supporting Information

The Supporting Information is available free of charge at https://pubs.acs.org/doi/10.1021/acsnano.0c09078.

Raman data of  $MoS_2$  capped by  $AlO_x$  without Al seed layer; modeling subthreshold swing (SS), charge trapping and doping; top-gate transistor measurements; transfer length method (TLM) measurements for contact and sheet resistance; transistor model with and without self-heating; effect of Al seed layer thickness on  $AlO_x$  doping; effect of  $H_2$  anneals (PDF)

## **AUTHOR INFORMATION**

## **Corresponding Author**

Eric Pop — Electrical Engineering and Materials Science and Engineering, Stanford University, Stanford, California 94305, United States; orcid.org/0000-0003-0436-8534; Email: epop@stanford.edu

#### **Authors**

Connor J. McClellan — Electrical Engineering, Stanford University, Stanford, California 94305, United States; orcid.org/0000-0002-8733-9968

Eilam Yalon — Electrical Engineering, Stanford University, Stanford, California 9430S, United States; ocid.org/ 0000-0001-7965-459X

Kirby K. H. Smithe – Electrical Engineering, Stanford University, Stanford, California 94305, United States Saurabh V. Suryavanshi – Electrical Engineering, Stanford University, Stanford, California 94305, United States

Complete contact information is available at: https://pubs.acs.org/10.1021/acsnano.0c09078

### **Author Contributions**

C.J.M., E.Y., and E.P. conceived the experiments and wrote the manuscript with input from all authors. K.K.H.S. grew the MoS<sub>2</sub>. C.J.M., S.S., and E.P. developed the subthreshold and drift current models. C.J.M. fabricated the devices. C.J.M. and E.Y. performed electrical, PL, and Raman characterizations.

#### Notes

The authors declare no competing financial interest.

## **ACKNOWLEDGMENTS**

Fabrication and measurements were performed in part at the Stanford Nanofabrication Facility (SNF) and the Stanford Nano Shared Facilities (SNSF), which received funding from the National Science Foundation (NSF) as part of National Nanotechnology Coordinated Infrastructure Award ECCS-1542152. This work was supported in part by ASCENT, one of six centers in JUMP, a Semiconductor Research Corporation (SRC) program sponsored by DARPA, and the Stanford SystemX Alliance. C.J.M. acknowledges support from the NSF Graduate Research Fellowship. K.K.H.S. acknowledges partial support from the Stanford Graduate Fellowship (SGF) program and NSF Graduate Research Fellowship under Grant No. DGE-114747.

## **REFERENCES**

- (1) Auth, C.; Aliyarukunju, A.; Asoro, M.; Bergstrom, D.; Bhagwat, V.; Birdsall, J.; Bisnik, N.; Buehler, M.; Chikarmane, V.; Ding, G. A 10 nm High Performance and Low-Power CMOS Technology Featuring 3rd Generation FinFET Transistors, Self-Aligned Quad Patterning, Contact over Active Gate and Cobalt Local Interconnects, IEEE International Electron Devices Meeting; IEEE, 2017; pp 29.21.21–29.21.24 DOI: 10.1109/IEDM.2017.8268472.

- (2) Bae, G.; Bae, D.-I.; Kang, M.; Hwang, S.; Kim, S.; Seo, B.; Kwon, T.; Lee, T.; Moon, C.; Choi, Y. *Impact of SOI thickness fluctuation on threshold voltage variation in ultra-thin body SOI MOSFETs.*, IEEE Trans. Nanotechnol; IEEE, 2018; pp 28.27.21–28.27.24 DOI: 10.1109/IEDM.2018.8614629.

- (3) Tsutsui, G.; Saitoh, M.; Nagumo, T.; Hiramoto, T. Impact of SOI thickness fluctuation on threshold voltage variation in ultra-thin body SOI MOSFETs. *IEEE Trans. Nanotechnol.* **2005**, *4* (3), 369–373.

- (4) Fiori, G.; Bonaccorso, F.; Iannaccone, G.; Palacios, T.; Neumaier, D.; Seabaugh, A.; Banerjee, S. K.; Colombo, L. Electronics

- Based on Two-Dimensional Materials. Nat. Nanotechnol. 2014, 9 (10), 768.

- (5) English, C. D.; Smithe, K. K.; Xu, R. L.; Pop, E. Approaching Ballistic Transport in Monolayer MoS<sub>2</sub> Transistors with Self-Aligned 10 nm Top Gates, IEEE International Electron Devices Meeting; IEEE, 2016; pp 5.6. 1–5.6. 4 DOI: 10.1109/IEDM.2016.7838355.

- (6) Baugher, B. W. H.; Churchill, H. O. H.; Yang, Y.; Jarillo-Herrero, P. Optoelectronic Devices Based on Electrically Tunable *P-N* Diodes in a Monolayer Dichalcogenide. *Nat. Nanotechnol.* **2014**, 9 (4), 262–267.

- (7) Wang, C.-H.; McClellan, C.; Shi, Y.; Zheng, X.; Chen, V.; Lanza, M.; Pop, E.; Wong, H.-S. P. 3D Monolithic Stacked 1T1R Cells Using Monolayer MoS<sub>2</sub> FET and hBN RRAM Fabricated at Low (150° C) Temperature, IEEE International Electron Devices Meeting; IEEE, 2018; pp 22.25. 21–22.25. 24 DOI: 10.1109/IEDM.2018.8614495.

- (8) Choi, M.; Park, Y. J.; Sharma, B. K.; Bae, S.-R.; Kim, S. Y.; Ahn, J.-H. Flexible Active-Matrix Organic Light-Emitting Diode Display Enabled by MoS<sub>2</sub> Thin-Film Transistor. *Science Advances* **2018**, *4* (4), eaas8721.

- (9) 2020 International Roadmap for Devices and Systems, https://irds.ieee.org/ (accessed 2020-12-07).

- (10) Zhao, P. D.; Kiriya, D.; Azcatl, A.; Zhang, C. X.; Tosun, M.; Liu, Y. S.; Hettick, M.; Kang, J. S.; McDonnell, S.; Santosh, K. C.; Guo, J. H.; Cho, K.; Wallace, R. M.; Javey, A. Air Stable *P*-Doping of WSe<sub>2</sub> by Covalent Functionalization. *ACS Nano* **2014**, 8 (10), 10808–10814.

- (11) Yu, L. L.; Zubair, A.; Santos, E. J. G.; Zhang, X.; Lin, Y. X.; Zhang, Y. H.; Palacios, T. High-Performance WSe<sub>2</sub> Complementary Metal Oxide Semiconductor Technology and Integrated Circuits. *Nano Lett.* **2015**, *15* (8), 4928–4934.

- (12) Fang, H.; Tosun, M.; Seol, G.; Chang, T. C.; Takei, K.; Guo, J.; Javey, A. Degenerate *N*-Doping of Few-Layer Transition Metal Dichalcogenides by Potassium. *Nano Lett.* **2013**, *13* (5), 1991–1995.

- (13) Kiriya, D.; Tosun, M.; Zhao, P. D.; Kang, J. S.; Javey, A. Air-Stable Surface Charge Transfer Doping of MoS<sub>2</sub> by Benzyl Viologen. *J. Am. Chem. Soc.* **2014**, *136* (22), 7853–7856.

- (14) Fathipour, S.; Pandey, P.; Fullerton-Shirey, S.; Seabaugh, A. Electric-Double-Layer Doping of WSe<sub>2</sub> Field-Effect Transistors Using Polyethylene-Oxide Cesium Perchlorate. *J. Appl. Phys.* **2016**, *120* (23), 234902.

- (15) Cai, L.; McClellan, C. J.; Koh, A. L.; Li, H.; Yalon, E.; Pop, E.; Zheng, X. Rapid Flame Synthesis of Atomically Thin MoO<sub>3</sub> Down to Monolayer Thickness for Effective Hole Doping of WSe<sub>2</sub>. *Nano Lett.* **2017**, *17* (6), 3854–3861.

- (16) Rai, A.; Valsaraj, A.; Movva, H. C. P.; Roy, A.; Ghosh, R.; Sonde, S.; Kang, S. W.; Chang, J. W.; Trivedi, T.; Dey, R.; Guchhait, S.; Larentis, S.; Register, L. F.; Tutuc, E.; Banerjee, S. K. Air Stable Doping and Intrinsic Mobility Enhancement in Monolayer Molybdenum Disulfide by Amorphous Titanium Suboxide Encapsulation. *Nano Lett.* **2015**, *15* (7), 4329–4336.

- (17) Leonhardt, A.; Chiappe, D.; Afanas'ev, V. V.; El Kazzi, S.; Shlyakhov, I.; Conard, T.; Franquet, A.; Huyghebaert, C.; De Gendt, S. Material-Selective Doping of 2D TMDC through Al<sub>x</sub>O<sub>y</sub> Encapsulation. *ACS Appl. Mater. Interfaces* **2019**, *11* (45), 42697–42707.

- (18) Yang, L. M.; Majumdar, K.; Liu, H.; Du, Y. C.; Wu, H.; Hatzistergos, M.; Hung, P. Y.; Tieckelmann, R.; Tsai, W.; Hobbs, C.; Ye, P. D. Chloride Molecular Doping Technique on 2D Materials: WS<sub>2</sub> and MoS<sub>2</sub>. *Nano Lett.* **2014**, *14* (11), 6275–6280.

- (19) Grenouillet, L.; Vinet, M.; Gimbert, J.; Giraud, B.; Noel, J.; Liu, Q.; Khare, P.; Jaud, M.; Le Tiec, Y.; Wacquez, R. *UTBB FDSOI Transistors with Dual STI for a Multi-V<sub>t</sub> Strategy at 20nm Node and Below,* IEEE International Electron Devices Meeting; IEEE, 2012; pp 3.6. 1–3.6. 4 DOI: 10.1109/IEDM.2012.6478974.

- (20) Smithe, K. K. H.; Suryavanshi, S. V.; Rojo, M. M.; Tedjarati, A. D.; Pop, E. Low Variability in Synthetic Monolayer MoS<sub>2</sub> Devices. *ACS Nano* **2017**, *11* (8), 8456–8463.

- (21) English, C. D.; Shine, G.; Dorgan, V. E.; Saraswat, K. C.; Pop, E. Improved Contacts to MoS<sub>2</sub> Transistors by Ultra-High Vacuum Metal Deposition. *Nano Lett.* **2016**, *16* (6), 3824–3830.

- (22) Song, S. M.; Cho, B. J. Contact Resistance in Graphene Channel Transistors. *Carbon Letters* **2013**, *14* (3), 162–170.

- (23) Fleetwood, D. M.; Senior, M. Border Traps" in MOS Devices. *IEEE Trans. Nucl. Sci.* **1992**, 39 (2), 269–271.

- (24) Fleetwood, D. M.; Winokur, P. S.; Reber, R. A.; Meisenheimer, T. L.; Schwank, J. R.; Shaneyfelt, M. R.; Riewe, L. C. Effects of Oxide Traps, Interface Traps, and "Border Traps" on Metal-Oxide-Semiconductor Devices. *J. Appl. Phys.* **1993**, *73* (10), 5058–5074.

- (25) Nguyen, L. D.; Larson, L. E.; Mishra, U. K. Ultra-High-Speed Modulation-Doped Field-Effect Transistors a Tutorial Review. *Proc. IEEE* **1992**, *80* (4), 494–518.

- (26) Kirsch, P. D.; Sivasubramani, P.; Huang, J.; Young, C.; Quevedo-Lopez, M.; Wen, H.; Alshareef, H.; Choi, K.; Park, C.; Freeman, K. Dipole Model Explaining High-K/Metal Gate Field Effect Transistor Threshold Voltage Tuning. *Appl. Phys. Lett.* **2008**, 92 (9), No. 092901.

- (27) Streetman, B.; Banerjee, S. Solid State Electronic Devices. 6; Prentice Hall:: United States, 2005; pp 300-311.

- (28) Xiong, K.; Robertson, J. Oxygen Vacancies in High Dielectric Constant Oxides La<sub>2</sub>O<sub>3</sub>, Lu<sub>2</sub>O<sub>3</sub>, and LaLuO<sub>3</sub>. *Appl. Phys. Lett.* **2009**, 95 (2), No. 022903.

- (29) Foster, A. S.; Gejo, F. L.; Shluger, A.; Nieminen, R. M. Vacancy and Interstitial Defects in Hafnia. *Phys. Rev. B: Condens. Matter Mater. Phys.* **2002**, *65* (17), 174117.

- (30) Dicks, O. A.; Cottom, J.; Shluger, A. L.; Afanas'ev, V. V. The Origin of Negative Charging in Amorphous Al<sub>2</sub>O<sub>3</sub> Films: The Role of Native Defects. *Nanotechnology* **2019**, *30* (20), 205201.

- (31) Ghatak, S.; Pal, A. N.; Ghosh, A. Nature of Electronic States in Atomically Thin MoS<sub>2</sub> Field-Effect Transistors. *ACS Nano* **2011**, *5* (10), 7707–7712.

- (32) Jena, D. Polarization Effects on Low-Field Transport & Mobility in III-V Nitride HEMTs. *Polarization Effects in Semi-conductors*; Springer US: Boston, MA, 2008; pp 161–216.

- (33) Lee, Y.; Fiore, S.; Luisier, M. In Ab Initio Mobility of Single-Layer MoS<sub>2</sub> and WS<sub>2</sub>: Comparison to Experiments and Impact on the Device Characteristics, IEEE International Electron Devices Meeting; IEEE, 2019; pp 24.24. 21–24.24. 24 DOI: 10.1109/IEDM19573.2019.8993477.

- (34) Suryavanshi, S. V.; Pop, E. S2DS: Physics-Based Compact Model for Circuit Simulation of Two-Dimensional Semiconductor Devices Including Non-Idealities. *J. Appl. Phys.* **2016**, *120* (22), 224503.

- (35) Jeon, T. S.; White, J. M.; Kwong, D. L. Thermal Stability of Ultrathin ZrO<sub>2</sub> Films Prepared by Chemical Vapor Deposition on Si(100). *Appl. Phys. Lett.* **2001**, *78* (3), 368–370.

- (36) Guha, S.; Gusev, E. P.; Okorn-Schmidt, H.; Copel, M.; Ragnarsson, L.-Å.; Bojarczuk, N. A.; Ronsheim, P. High Temperature Stability of Al<sub>2</sub>O<sub>3</sub> Dielectrics on Si: Interfacial Metal Diffusion and Mobility Degradation. *Appl. Phys. Lett.* **2002**, *81* (16), 2956–2958.

- (37) Vaziri, S.; Chen, V.; Cai, L.; Jiang, Y.; Chen, M. E.; Grady, R. W.; Zheng, X.; Pop, E. Ultrahigh Doping of Graphene Using Flame-Deposited MoO<sub>3</sub>. *IEEE Electron Device Lett.* **2020**, 41 (10), 1592–1595.

- (38) Schauble, K.; Zakhidov, D.; Yalon, E.; Deshmukh, S.; Grady, R. W.; Cooley, K. A.; McClellan, C. J.; Vaziri, S.; Passarello, D.; Mohney, S. E. Uncovering the Effects of Metal Contacts on Monolayer MoS<sub>2</sub>. ACS Nano **2020**, *14* (11), 14798–14808.

- (39) Wu, C.-L.; Yuan, H.; Li, Y.; Gong, Y.; Hwang, H. Y.; Cui, Y. Gate-Induced Metal—Insulator Transition in MoS<sub>2</sub> by Solid Superionic Conductor LaF<sub>3</sub>. *Nano Lett.* **2018**, *18* (4), 2387–2392.

- (40) Allain, A.; Kang, J. H.; Banerjee, K.; Kis, A. Electrical Contacts to Two-Dimensional Semiconductors. *Nat. Mater.* **2015**, *14* (12), 1195–1205.

- (41) Arutchelvan, G.; de la Rosa, C. J. L.; Matagne, P.; Sutar, S.; Radu, I.; Huyghebaert, C.; De Gendt, S.; Heyns, M. From the Metal

- to the Channel: A Study of Carrier Injection through the Metal/2D MoS<sub>2</sub> Interface. *Nanoscale* **2017**, *9* (30), 10869–10879.

- (42) Szabó, Á.; Jain, A.; Parzefall, M.; Novotny, L.; Luisier, M. Electron Transport through Metal/MoS2 Interfaces: Edge-or Area-Dependent Process? *Nano Lett.* **2019**, *19* (6), 3641–3647.

- (43) Smithe, K. K.; English, C. D.; Suryavanshi, S. V.; Pop, E. High-Field Transport and Velocity Saturation in Synthetic Monolayer MoS<sub>2</sub>. *Nano Lett.* **2018**, *18* (7), 4516–4522.

- (44) Frindt, R. F. Single Crystals of MoS<sub>2</sub> Several Molecular Layers Thick. *J. Appl. Phys.* **1966**, 37 (4), 1928–1929.

- (45) Yu, J.; Liu, G.; Sumant, A. V.; Goyal, V.; Balandin, A. A. Graphene-on-Diamond Devices with Increased Current-Carrying Capacity: Carbon sp<sup>2</sup>-on-sp<sup>3</sup> Technology. *Nano Lett.* **2012**, *12* (3), 1603–1608.

- (46) Chen, Y.-F.; Fuhrer, M. Electric-Field-Dependent Charge-Carrier Velocity in Semiconducting Carbon Nanotubes. *Phys. Rev. Lett.* **2005**, 95 (23), 236803.

- (47) Khater, M. H.; Zhang, Z.; Cai, J.; Lavoie, C.; D'Emic, C.; Yang, Q.; Yang, B.; Guillorn, M.; Klaus, D.; Ott, J. A. High-K Metal-Gate Fully Depleted SOI CMOS with Single-Silicide Schottky Source/Drain with Sub-30-nm Gate Length. *IEEE Electron Device Lett.* **2010**, 31 (4), 275–277.

- (48) Zota, C. B.; Lindelow, F.; Wernersson, L.; Lind, E. InGaAs nanowire MOSFETs with  $I_{\rm ON}=555~\mu{\rm A}/\mu{\rm m}$  at  $I_{\rm OFF}=100~{\rm nA}/\mu{\rm m}$  and  $V_{\rm DD}=0.5~V.$  Symp. VLSI Technol. Dig. Tech. 2016 DOI: 10.1109/VLSIT.2016.7573418.

- (49) Rakheja, S.; Lundstrom, M. S.; Antoniadis, D. A. An Improved Virtual-Source-Based Transport Model for Quasi-Ballistic Transistors—Part I: Capturing Effects of Carrier Degeneracy, Drain-Bias Dependence of Gate Capacitance, and Nonlinear Channel-Access Resistance. *IEEE Trans. Electron Devices* **2015**, *62* (9), 2786–2793.

- (50) Yalon, E.; Aslan, Ö. B.; Smithe, K. K. H.; McClellan, C. J.; Suryavanshi, S. V.; Xiong, F.; Sood, A.; Neumann, C. M.; Xu, X.; Goodson, K. E.; Heinz, T. F.; Pop, E. Temperature Dependent Thermal Boundary Conductance of Monolayer MoS<sub>2</sub> by Raman Thermometry. ACS Appl. Mater. Interfaces 2017, 9 (49), 43013–43020.

- (51) Taur, Y.; Ning, T. H. Fundamentals of Modern VLSI Devices 2; Cambridge University Press, 2013; pp 148–196.

- (52) Nathawat, J.; Smithe, K.; English, C.; Yin, S.; Dixit, R.; Randle, M.; Arabchigavkani, N.; Barut, B.; He, K.; Pop, E.; Bird, J. Transient Hot-Carrier Dynamics and Intrinsic Velocity Saturation in Monolayer MoS<sub>2</sub>. *Physical Review Materials* **2020**, *4* (1), No. 014002.

- (53) Liu, Y.; Jian, G.; Ye-Cun, W.; Enbo, Z. O.; W, N.; Qiyuan, H.; Hao, W.; Hung-Chieh, C.; Yang, X.; Imran, S.; Yu, H.; Xiangfeng, D. Pushing the Performance Limit of Sub-100 nm Molybdenum Disulfide Transistors. *Nano Lett.* **2016**, *16* (10), 6337–6342.

- (54) Suryavanshi, S. V.; Gabourie, A. J.; Barati Farimani, A.; Pop, E. Thermal Boundary Conductance of Two-Dimensional MoS<sub>2</sub> Interfaces. *J. Appl. Phys.* **2019**, *126* (5), No. 055107.

- (55) Islam, S.; Li, Z.; Dorgan, V. E.; Bae, M.-H.; Pop, E. Role of Joule Heating on Current Saturation and Transient Behavior of Graphene Transistors. *IEEE Electron Device Lett.* **2013**, 34 (2), 166–168.

- (56) Singh, N.; Agarwal, A.; Bera, L. K.; Liow, T. Y.; Yang, R.; Rustagi, S. C.; Tung, C. H.; Kumar, R.; Lo, G. Q.; Balasubramanian, N.; Kwong, D. L. High-Performance Fully Depleted Silicon-Nanowire (Diameter ≤ 5 nm) Gate-All-Around CMOS Devices. *IEEE Electron Device Lett.* **2006**, 27 (5), 383−386.

- (57) Frank, D. J.; Dennard, R. H.; Nowak, E.; Solomon, P. M.; Taur, Y.; Wong, H. S. P. Device Scaling Limits of Si Mosfets and Their Application Dependencies. *Proc. IEEE* **2001**, *89* (3), 259–288.

- (58) McClellan, C. J.; Suryavanshi, S. V.; English, C. D.; Smithe, K. K. H.; Bailey, C. S.; Grady, R. W.; Pop, E. 2D Device Trends. http://2d.stanford.edu (accessed 2020-10-20).

- (59) Kim, S.; Junghyo, N.; Insun, J.; Davood, S.; Luigi, C.; Zhen, Y.; Emanuel, T.; K, B. S. Realization of a High Mobility Dual-Gated Graphene Field-Effect Transistor with Al<sub>2</sub>O<sub>3</sub> Dielectric. *Appl. Phys. Lett.* **2009**, *94* (6), No. 062107.

- (60) Chandrasekhar, M.; Renucci, J.; Cardona, M. Effects of Interband Excitations on Raman Phonons in Heavily Doped N-Si. Phys. Rev. B: Condens. Matter Mater. Phys. 1978, 17 (4), 1623.

- (61) Tsang, J.; Freitag, M.; Perebeinos, V.; Liu, J.; Avouris, P. Doping and Phonon Renormalization in Carbon Nanotubes. *Nat. Nanotechnol.* **2007**, 2 (11), 725–730.

- (62) Chakraborty, B.; Bera, A.; Muthu, D.; Bhowmick, S.; Waghmare, U. V.; Sood, A. K. Symmetry-Dependent Phonon Renormalization in Monolayer MoS<sub>2</sub> Transistor. *Phys. Rev. B: Condens. Matter Mater. Phys.* **2012**, 85 (16), 161403.

- (63) Yalon, E.; McClellan, C. J.; Smithe, K. K. H.; Munoz Rojo, M.; Xu, R. L.; Suryavanshi, S. V.; Gabourie, A. J.; Neumann, C. M.; Xiong, F.; Farimani, A. B.; Pop, E. Energy Dissipation in Monolayer MoS<sub>2</sub> Electronics. *Nano Lett.* **2017**, *17* (6), 3429–2433.

- (64) Sanne, A.; Rudresh, G.; Amritesh, R.; Nagavalli, Y. M.; Heon, S. S.; Ankit, S.; Karalee, J.; Leo, M.; Rajesh, R.; Deji, A.; Sanjay, B. Radio Frequency Transistors and Circuits Based on CVD MoS<sub>2</sub> FETs. *Nano Lett.* **2015**, *15* (8), 5039–5045.

- (65) Li, L.; Engel, M.; Farmer, D. B.; Han, S.-j.; Wong, H.-S. P. High-Performance *P*-Type Black Phosphorus Transistor with Scandium Contact. *ACS Nano* **2016**, *10* (6), 4672–4677.

- (66) Yang, L.; Qiu, G.; Si, M.; Charnas, A.; Milligan, C.; Zemlyanov, D.; Zhou, H.; Du, Y.; Lin, Y.; Tsai, W. Few-Layer Black Phosporous PMOSFETs with BN/Al<sub>2</sub>O<sub>3</sub> Bilayer Gate Dielectric: Achieving  $I_{on}$ =850  $\mu$ A/ $\mu$ m,  $G_m$ =340  $\mu$ S/ $\mu$ m, and  $R_c$ =0.58 k $\Omega$ · $\mu$ m, IEEE International Electron Devices Meeting; IEEE, 2016; pp 5.5. 1–5.5. 4 DOI: 10.1109/IEDM.2016.7838354.

- (67) Yang, L.; Lee, R.; Rao, S. P.; Tsai, W.; Ye, P. 10 nm Nominal Channel Length MoS<sub>2</sub> FETs with EOT 2.5 nm and 0.52 mA/µm Drain Current, Device Research Conference (DRC), 2015 73rd Annual; IEEE, 2015; pp 237–238 DOI: 10.1109/DRC.2015.7175655.

- (68) Chou, A.-S.; Shen, P.-C.; Cheng, C.-C.; Lu, L.-S.; Chueh, W.-C.; Li, M.-Y.; Pitner, G.; Chang, W.-H.; Wu, C.-I.; Kong, J.; Li, L.-J.; Wong, H.-S. P. In High On-Current 2D NFET of 390 uA/um at  $V_{ds} = 1V$  Using Monolayer CVD  $MoS_2$  without Intentional Doping, 2020 IEEE Symposium on VLSI Technology; IEEE, 2020 DOI: 10.1109/VLSITechnology18217.2020.9265040.

- (69) Tosun, M.; Chan, L.; Amani, M.; Roy, T.; Ahn, G. H.; Taheri, P.; Carraro, C.; Ager, J. W.; Maboudian, R.; Javey, A. Air-Stable *N*-Doping of WSe<sub>2</sub> by Anion Vacancy Formation with Mild Plasma Treatment. *ACS Nano* **2016**, *10* (7), 6853–6860.

- (70) Yamamoto, M.; Nakaharai, S.; Ueno, K.; Tsukagoshi, K. Self-Limiting Oxides on WSe<sub>2</sub> as Controlled Surface Acceptors and Low-Resistance Hole Contacts. *Nano Lett.* **2016**, *16* (4), 2720–2727.

- (71) Liu, B.; Ma, Y.; Zhang, A.; Chen, L.; Abbas, A. N.; Liu, Y.; Shen, C.; Wan, H.; Zhou, C. High-Performance WSe<sub>2</sub> Field-Effect Transistors *via* Controlled Formation of In-Plane Heterojunctions. *ACS Nano* **2016**, *10* (5), 5153–5160.

- (72) Lockhart de la Rosa, C. J.; Nourbakhsh, A.; Heyne, M.; Asselberghs, I.; Huyghebaert, C.; Radu, I.; Heyns, M.; De Gendt, S. Highly Efficient and Stable MoS<sub>2</sub> FETs with Reversible *N*-Doping Using a Dehydrated Poly(Vinyl-Alcohol) Coating. *Nanoscale* **2017**, 9 (1), 258–265.

- (73) Cao, W.; Liu, W.; Kang, J.; Banerjee, K. An Ultra-Short Channel Monolayer MoS<sub>2</sub> FET Defined by the Curvature of a Thin Nanowire. *IEEE Electron Device Lett.* **2016**, 37 (11), 1497–1500.

- (74) Nourbakhsh, A.; Zubair, A.; Sajjad, R. N.; Tavakkoli K. G., A.; Chen, W.; Fang, S.; Ling, X.; Kong, J.; Dresselhaus, M. S.; Kaxiras, E. MoS<sub>2</sub> Field-Effect Transistor with Sub-10 nm Channel Length. *Nano Lett.* **2016**, *16* (12), 7798–7806.

- (75) Lembke, D.; Kis, A. Breakdown of High-Performance Monolayer MoS<sub>2</sub> Transistors. ACS Nano 2012, 6 (11), 10070–10075. (76) Smithe, K. K.; English, C. D.; Suryavanshi, S. V.; Pop, E. Intrinsic Electrical Transport and Performance Projections of Synthetic Monolayer MoS<sub>2</sub> Devices. 2D Mater. 2017, 4 (1), No. 011009.

- (77) Yu, Z.; Zhu, Y.; Li, W.; Shi, Y.; Zhang, G.; Chai, Y.; Wang, X. Toward High-Mobility and Low-Power 2D MoS<sub>2</sub> Field-Effect Transistors,

IEEE International Electron Devices Meeting; IEEE, 2018; pp 22.24. 21–22.24. 24 DOI: 10.1109/IEDM.2018.8614644. (78) Ashokbhai Patel, K.; Grady, R. W; Smithe, K. K H; Pop, E.; Sordan, R. Ultra-Scaled MoS $_2$  Transistors and Circuits Fabricated without Nanolithography. 2D Mater. 2020, 7 (1), No. 015018.

# Supporting Information for:

# High Current Density in Monolayer MoS<sub>2</sub> Doped by AlO<sub>x</sub>

Connor J. McClellan<sup>1</sup>, Eilam Yalon<sup>1,2</sup>, Kirby K.H. Smithe<sup>1</sup>, Saurabh V. Suryavanshi<sup>1</sup>, and Eric Pop<sup>1,3,\*</sup>

# Section S1. Raman and PL Data on Doping

We used Raman spectroscopy and photoluminescence (PL) measurements for initial characterization of AlO<sub>x</sub>-doped MoS<sub>2</sub>. Figure 1d from the main text displays Raman spectra of MoS<sub>2</sub> before and after doping with the AlO<sub>x</sub> encapsulation layer. We observe red-shifts in both the E' and A<sub>1</sub>' peaks after AlO<sub>x</sub> deposition. The A<sub>1</sub>' peak is expected to red-shift with increasing carrier concentration of MoS<sub>2</sub>, and the observed 0.7 cm<sup>-1</sup> shift corresponds to induced carrier density  $\Delta n \sim 3.2 \times 10^{12}$  cm<sup>-2</sup>, lower than  $\Delta n \sim 8.6 \times 10^{12}$  cm<sup>-2</sup> obtained by electrical characterization. However, we note the electrical measurement is more accurate than the Raman estimate, due to the limited spectrometer resolution.

The E' peak of monolayer (1L) MoS<sub>2</sub> is sensitive to strain<sup>2</sup> but its asymmetry seen in main text Fig. 1d is consistent with a doping-induced Fano effect, which has been previously noted in several other semiconductors with high doping.<sup>3,4</sup> Raman measurements of MoS<sub>2</sub> capped by 150°C ALD-deposited AlO<sub>x</sub> without the Al seed layer (Fig. S1) show no shift of the A<sub>1</sub>' peak and no asymmetry of the E' peak, suggesting that the doping effect is enhanced with the Al seed layer (which subsequently oxidizes) for conformal deposition of AlO<sub>x</sub> and doping of the underlying MoS<sub>2</sub>.

PL measurements in main text Fig. 1c show a decrease and slight red shift of MoS<sub>2</sub> PL after AlO<sub>x</sub> capping. The shift is consistent with the effects of tensile strain<sup>2</sup> and dielectric screening<sup>5</sup> that decrease the MoS<sub>2</sub> optical band gap. In addition, the broadening of the PL peak indicates higher rate of non-radiative recombination, ostensibly due to the presence of charge and defects in the AlO<sub>x</sub>.

**Fig. S1 Raman Spectra.** Raman spectra of bare MoS<sub>2</sub> before AlO<sub>x</sub> and after 150°C ALD-AlO<sub>x</sub> deposition *without* Al seeding layer. Contrasting with the Raman spectra in main text Fig. 1d, not using the Al seeding layer causes no change in the A<sub>1</sub>' peak and no Fano asymmetry of the E' peak.

<sup>&</sup>lt;sup>1</sup>Electrical Engineering, Stanford University, Stanford, CA 94305, USA

<sup>&</sup>lt;sup>2</sup>Present address: Electrical Engineering, Technion, Israel Institute of Technology, Haifa, 32000, Israel

<sup>&</sup>lt;sup>3</sup>Materials Science and Engineering, Stanford University, Stanford, CA 94305, USA

<sup>\*</sup>Corresponding author: epop@stanford.edu

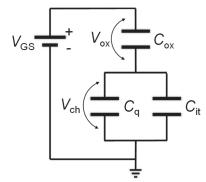

# Section S2. Extraction of Interface Trap Density from Change in Subthreshold Swing

We estimate the interface trap density ( $D_{it}$ ) with the standard model of subthreshold current in field-effect transistors (FETs), aided by the diagram in Fig. S2. The subthreshold swing is:<sup>6,7</sup>

$$SS \approx (\ln 10) \frac{k_{\rm B}T}{q} \left( 1 + \frac{c_{\rm it} + c_{\rm q}}{c_{\rm ox}} \right)$$

(E1)

where  $k_{\rm B}$  is the Boltzmann constant, T is the temperature, q is the elementary charge,  $C_{\rm it}$  is the interface trap capacitance ( $C_{\rm it} = q^2 D_{\rm it}$ ),  $C_{\rm q}$  is the MoS<sub>2</sub> quantum capacitance, and  $C_{\rm ox}$  is the oxide capacitance ( $C_{\rm ox} = \epsilon_{\rm ox}/t_{\rm ox} \approx 115~\rm nF/cm^2$  for our 30 nm SiO<sub>2</sub> back-gate oxide). We ignore the depletion capacitance ( $C_{\rm D} = \epsilon_{\rm MoS2}/t_{\rm mos2}$ ) for monolayer MoS<sub>2</sub>, as it will be much larger than the series  $C_{\rm q}$  and  $C_{\rm it}$ . As the Al deposition (on top) will not affect  $C_{\rm ox}$  (bottom) or  $C_{\rm q}$ , we can approximate the change in  $D_{\rm it}$  due to AlO<sub>x</sub> capping of MoS<sub>2</sub> from the change in SS, resulting in:

$$\Delta D_{\rm it} \approx \frac{\Delta SS \times C_{\rm ox}}{(\ln 10)k_{\rm B}T} \tag{E2}$$

This equation stipulates that the SS of MoS<sub>2</sub> FETs depends on the interface trap density ( $D_{it}$ ), but is independent of the mobile charge concentration and should not change with doping.

Fig. S2. MoS<sub>2</sub> FET Capacitance Schematic. Circuit schematic of the monolayer MoS<sub>2</sub> transistor including quantum capacitance ( $C_q$ ) and interface trap capacitance ( $C_{it}$ ) effects on the gate control.  $V_{ch}$  and  $V_{ox}$  are the voltages dropped across the channel and oxide, respectively.

## Section S3. Modeling of Charge Trapping and Charge Doping

To illustrate the difference between trapping and doping, we use a drift-diffusion model<sup>6</sup> to capture the transfer characteristics of a 2D *n*-type FET with both interface traps and doping. The classical drift current<sup>7</sup> in the linear region describes electron motion from source to drain:

$$I_{\text{drift}} = qnv_{\text{d}} \tag{E3}$$

$$n = C_{\text{ox}} \left( V_{\text{GS}} - V_{\text{T}} - \frac{V_{DS}}{2} \right) / q \tag{E4}$$

$$v_{\rm d} = \frac{\mu_{\rm eff} F}{\left[1 + \left(\frac{\mu_{\rm eff} F}{\nu_{\rm sat}}\right)^{\gamma}\right]^{1/\gamma}} \tag{E5}$$

where  $V_T$  is the threshold voltage, n is the average electron density between source and drain,  $v_d$  is the average drift velocity in the MoS<sub>2</sub> channel, F is the average lateral field  $F \approx (V_{DS} - 2I_DR_C)/L$ ),  $v_{sat}$  is the saturation velocity of MoS<sub>2</sub> ( $\approx 4 \times 10^6$  cm/s),  $\gamma$  is an empirical fitting parameter ( $\gamma \approx 5$ ) and  $\mu_{eff}$  is the effective electron mobility.<sup>8</sup>

However, modeling the subthreshold diffusion current is difficult in a monolayer 2D transistor, as the depletion capacitance is large and the quantum capacitance ( $C_q$ ) dominates. Ref. 9 gave equations for  $C_q$  with a known Fermi energy ( $E_F$ ), although  $E_F$  is not easily estimated in experimental devices. As our goal is modeling the effects of traps on the change in subthreshold current, we estimate  $C_q$  from the undoped 2D FET using eq. E1 over a  $V_{GS}$  range, and then calculate  $E_F$  using Ref. 9. With the extracted  $E_F$  for the undoped MoS<sub>2</sub> FET, we then incorporate trap levels with delta distributions in computing  $C_q$  using eq. 4 of Suryavanshi *et al.* Thus, the subthreshold diffusion current is:

$$I_{\text{diff}} = \frac{q D_n N_{2D}}{L} \ln \left( \frac{\exp\left[\frac{q (V_{GS} - V_T)}{C_T k_B T}\right] + 1}{\exp\left[\frac{q (V_{GS} - V_T - V_{DS})}{C_T k_B T}\right] + 1} \right)$$

(E6)

where  $D_n = (k_B T/q) \mu_{\text{eff}}$  is the electron diffusion coefficient,  $N_{2D}$  is the 2D density of states from equation 2 of Suryavanshi *et al.*<sup>6</sup> and  $C_r$  is the normalized capacitance term  $[C_r = 1 + (C_q + C_{it})/C_{ox}]$ . The total current is then simply  $I_D = I_{\text{drift}} + I_{\text{diff}}$  from equations (E3) and (E6) above.

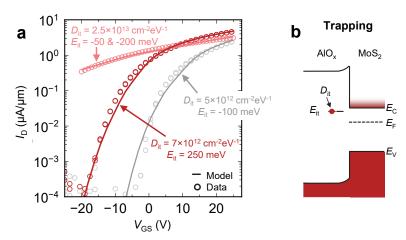

For the simulations shown in the main text Fig. 2 we use the following parameters, also labeled on Fig. S3. For the initial MoS<sub>2</sub> device without AlO<sub>x</sub> capping we use  $V_T = 10$  V,  $\mu_{eff} = 33$  cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, and a native interface trap density  $D_{it} = 5 \times 10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup> at an energy level  $E_{it} = -100$  meV (i.e. 100 meV below the MoS<sub>2</sub> conduction band) to capture the traps already present within the CVD-grown MoS<sub>2</sub> or at the SiO<sub>2</sub>/MoS<sub>2</sub> interface. This  $D_{it}$  at  $E_{it} = -100$  meV is present in all our simulations, as these traps remain at the SiO<sub>2</sub>/MoS<sub>2</sub> interface.

After deposition of AlO<sub>x</sub>, we add two trap levels at  $E_{it} = -200$  meV and -50 meV, each with  $D_{it} = 2.5 \times 10^{13}$  cm<sup>-2</sup>eV<sup>-1</sup> without changing other model parameters (i.e. constant  $V_T$  and  $\mu_{eff}$ ). To model the channel after 200°C annealing in N<sub>2</sub>, we remove the trap levels from  $E_{it} = -200$  meV and -50 meV, but add an additional trap level at  $E_{it} = 250$  meV (above the conduction band) with  $D_{it} = 7 \times 10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup>. These parameters are listed on and correspond to the three scenarios labeled in Fig. S3.

**Fig. S3. Experimental** *I-V* and Trap Modeling. (a) Measured  $I_D$  vs. back-gate  $V_{GS}$  (symbols) shown in main text Fig. 2b. Simulations (lines) are shown with parameters used. Colors are consistent with Fig. 2 in the main text: (1) gray is the bare MoS<sub>2</sub> device before AlO<sub>x</sub> deposition, (2) light red is right after deposition, and (3) dark red is after the anneal step. We note the negative threshold voltage shift after AlO<sub>x</sub> deposition (due to doping), and the recovery of the good on/off ratio after the anneal step. (b) Band diagram showing  $E_{it}$  and  $D_{it}$  in the AlO<sub>x</sub> on MoS<sub>2</sub> in the trapping state, i.e.  $E_{it}$  within the MoS<sub>2</sub> band gap. The charge trap distribution is incorporated in the model as a delta function  $D_{it}\delta(E-E_{it})$ , as described by Suryavanshi *et al.*<sup>6</sup>

# Section S4. Top-Gate Measurements with Doping AlO<sub>x</sub> Layer

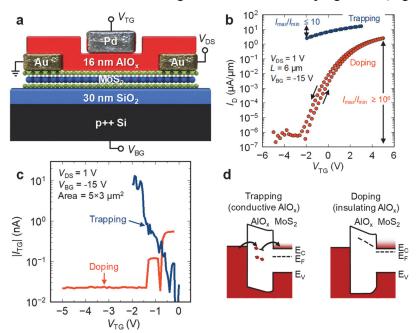

We also evaluate the  $AlO_x$  capping layer as a top-gate dielectric (Fig. S4a). The double-gate transistor has a source-drain contact separation  $L=6~\mu m$ , top gate length  $L_G=5~\mu m$ , and channel width  $W=3~\mu m$ , confirmed by atomic force microscopy (AFM). The Pd top-gate was defined using electron beam lithography and deposited with electron-beam evaporation. After the electron-beam evaporation step, we observed that all devices on the sample displayed trapping-like characteristics (Fig. S4b). The degradation of top-gate control originates from an increase in the density of mid-gap defect states due to oxide damage induced by the high energy X-rays emitted during electron-beam evaporation. However, a 40 min 200°C  $N_2$  anneal recovers the gate control to the "doping" state (Fig. S4b).

**Fig. S4. Top-Gate Measurements:** (a) Schematic of dual-gated MoS<sub>2</sub> FET, using the AlO<sub>x</sub> layer as a top-gate dielectric. (b) Measured  $I_D$  vs.  $V_{TG}$  data showing the large  $I_{on}/I_{off}$  of the doping state and small  $I_{on}/I_{off}$  of the trapping state, similar to data using the back-gate. The arrows mark forward and backward sweeps, indicating relatively low hysteresis. (c) Top-gate leakage measurements showing that the AlO<sub>x</sub> dielectric with a large trap concentration ("trapping") is more conductive than with low trap concentration ("doping"). (d) Energy band diagram showing how mid-gap traps in the AlO<sub>x</sub> lead to trap-assisted tunneling and high gate leakage, but higher-energy state traps (in the "doping" state of the oxide) do not.

Fig. S4c displays the measured top-gate leakage current ( $I_{TG}$ ) for the trapping and doping states. Large  $I_{TG}$  is measured for the trapping state, limiting the top-gate voltage ( $V_{TG}$ ) sweep from only -2 V to 3 V in Fig. S4b. For the doping state,  $I_{TG}$  is reduced to <10 pA, allowing for a  $V_{TG}$  sweep from -5 V to 5 V. The large contrast in  $I_{TG}$  between trapping and doping offers insight into the state of the AlO<sub>x</sub> in these two cases, illustrated with schematic energy band diagrams in Fig. S4d. AlO<sub>x</sub> in the trapping state is leaky due to defects that promote electron conduction and trap MoS<sub>2</sub> electrons, degrading FET performance and increasing  $I_{TG}$  by trap-assisted tunneling. AlO<sub>x</sub> in the doping state has higher defect energy levels, above the MoS<sub>2</sub> conduction band, reducing trap-assisted tunneling and decreasing  $I_{TG}$ . The lower  $I_{TG}$  indicates that post-anneal AlO<sub>x</sub> can be effectively used to dope the underlying 2D semiconductor while also serving as a top-gate dielectric, allowing for process integration of doping and dielectric formation. However, future studies will need to reduce the physical (and equivalent) oxide thickness of the top-gate dielectric, and/or combine it with an additional layer which has a higher dielectric constant (e.g. HfO<sub>2</sub>). This is needed to reduce the operating gate voltage of MoS<sub>2</sub> transistors.

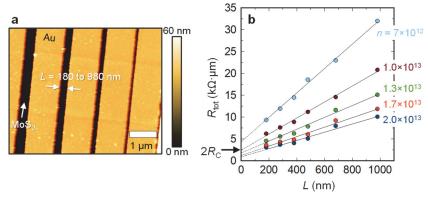

# **Section S5. Transfer Length Method Measurements**

We use the transfer length method (TLM)<sup>12</sup> to obtain both sheet and contact resistance of our MoS<sub>2</sub> after doping with the AlO<sub>x</sub> capping layer. Fig. S5a shows a TLM structure with six channel lengths of 180, 280, 380, 480, 680, and 980 nm (measured by AFM). Fig. S5b plots the measured resistance ( $R_{tot}$ ) vs. channel length (L), showing the expected linear scaling. Here, we account for the (small) Au wiring resistance in the TLM, reducing the measured resistance of all devices by 5  $\Omega$  (or 10  $\Omega$ · $\mu$ m normalized by the 2  $\mu$ m channel width), which was estimated from shorted Au test structures. The sheet resistance ( $R_{sh}$ ) and contact resistance ( $R_{c}$ ) are extracted from the slope and vertical intercept of the TLM plot as:

$$R_{\text{tot}} = R_{\text{sh}}L + 2R_{\text{C}}.\tag{E7}$$

With the extracted  $R_{\rm sh}$ , the effective mobility ( $\mu_{\rm eff}$ ) is obtained as:

$$\mu_{\rm eff} = (qnR_{\rm sh})^{-1} \tag{E8}$$

where the carrier density n is estimated from the gate voltage in eq. E4. We note that due to uncertainties in the threshold voltage  $V_T$  (and due to small contributions from  $C_q \le 5\%$  at  $n \ge 5 \times 10^{12}$  cm<sup>-2</sup>) the carrier density n and therefore the mobility are more accurately estimated at larger  $V_{GS}$ . There are also small  $V_T$  variations between the different channels within the TLM structure, and thus the TLM extraction is performed at the same gate overdrive ( $V_{GS} - V_T$ ) for each individual channel. Additional details of TLM extraction, uncertainty estimates, and other pitfalls are given by English  $et\ al.$  12

**Fig. S5. TLM Measurements:** (a) AFM of TLM structure on monolayer MoS<sub>2</sub>, from main text Fig. 1b. (b) Measured  $R_{\text{tot}}$  vs. L, used for extracting  $R_{\text{C}}$  and  $R_{\text{sh}}$  at different carrier densities. All lengths were measured by SEM and AFM, confirming channel lengths ~20 nm smaller than target values (i.e. L = 980 nm, 680 nm, 480 nm, etc.). The 380 nm channel had slightly better characteristics than other channel lengths (i.e. lower  $V_{\text{T}}$ ) while 680 nm was slightly worse, causing some of the uncertainty in the  $R_{\text{C}}$  extraction.

The effective mobility  $\mu_{\rm eff}$  may be underestimated vs. the Hall mobility because the extraction of n may be overestimated due to traps in the MoS<sub>2</sub> and/or surrounding dielectrics, <sup>13,14</sup> as discussed in the main text. However,  $\mu_{\rm eff}$  is an effective mobility that captures how well the gate controls  $R_{\rm sh}$  of the MoS<sub>2</sub> (independent of  $R_{\rm C}$ ), and is also used to calculate the current with eqs. E3-E5. Thus,  $\mu_{\rm eff}$  is the correct metric which captures the transconductance and net current flow in these transistors.

From the TLM data, we can also extract the current transfer length ( $L_{\rm T}$ ), which is the characteristic distance that electrons travel in the semiconductor under the metal contact before flowing up into the metal. This can be simply estimated as  $L_{\rm T} = R_{\rm C}/R_{\rm sh,c}$  where  $R_{\rm sh,c}$  is the sheet resistance of the MoS<sub>2</sub> under the contact. For simplicity, we use our average channel  $R_{\rm sh} \approx 9 \ {\rm k}\Omega/\Box$  but the actual  $R_{\rm sh,c}$  could be higher due to (some) metal evaporation damage to the MoS<sub>2</sub> under the metal contact. From this, we estimate an upper bound of  $L_{\rm T} = 53$  nm at  $n = 2 \times 10^{13}$  cm<sup>-2</sup>, indicating the contact length of our devices could be scaled to ~50 nm before contact current crowding effects become non-negligible.

# Section S6. High On-Current and High On/Off

While achieving high drain current in transistors can decrease circuit delay, transistors must also have a high  $I_{\rm on}/I_{\rm off}$  ratio to maintain low leakage current. Fig. S6 plots the measured log-scale  $I_{\rm D}$  vs.  $V_{\rm GS}$  of a doped MoS<sub>2</sub> FET showing  $I_{\rm on}/I_{\rm off} > 10^6$  at both  $V_{\rm DS} = 2$  V and 5 V. These results contrast many previous reports of high current in 2D material transistors, where increasing lateral field (i.e.  $V_{\rm DS}$ ) results in an exponential increase in  $I_{\rm off}$ , reducing  $I_{\rm on}/I_{\rm off}$ . The increase in  $I_{\rm off}$  is common in small band gap material transistors, such as black phosphorus, where larger lateral field increases band-to-band leakage current. Our devices can maintain a high  $I_{\rm on}/I_{\rm off}$  as monolayer MoS<sub>2</sub> has a larger band gap ( $E_{\rm G} > 2$  eV)<sup>15</sup> reducing band-to-band tunneling effects.

**Fig. S6. High-Current**  $I_D$ - $V_{GS}$ : Measured log  $I_D$  vs.  $V_{GS}$  of a highly doped MoS<sub>2</sub> FET showing  $I_{on}/I_{off} > 10^6$  at  $V_{DS} = 2$  V and 5 V. The channel length L = 380 nm and back-gate oxide thickness  $t_{ox} = 30$  nm.

# Section S7. Thermal Modeling of MoS<sub>2</sub> FETs

We use a compact thermal model of 2D material FETs to estimate the effects of self-heating on device performance. We first calculate the thermal conductance per unit length (g) and thermal resistance  $(R_{th})$  from MoS<sub>2</sub> to the Si substrate back-side from the equations:<sup>6</sup>

$$g = \frac{R_{\text{Cox}}}{W} + \left\{ \frac{\pi \kappa_{\text{ox}}}{\ln[6(\frac{t_{\text{ox}}}{W} + 1)]} + \frac{\kappa_{\text{ox}}}{t_{\text{ox}}} W \right\}^{-1} + \frac{1}{2k_{\text{si}}} \left(\frac{L}{W_{\text{eff}}}\right)^{\frac{1}{2}}$$

(E9)

$$R_{\rm th} = \frac{1}{aL} \tag{E10}$$

where  $R_{\text{Cox}}$  is the thermal boundary resistance between MoS<sub>2</sub> and SiO<sub>2</sub>, W is the width of the MoS<sub>2</sub> channel,  $\kappa_{\text{ox}}$  is the thermal conductivity of SiO<sub>2</sub>,  $t_{\text{ox}}$  is the thickness of the SiO<sub>2</sub>,  $\kappa_{\text{si}}$  is the thermal conductivity of the highly doped Si substrate,  $W_{\text{eff}}$  is the effective width of the MoS<sub>2</sub> device including thermal spreading<sup>16</sup> into the SiO<sub>2</sub> ( $W_{\text{eff}} \approx W + 2t_{\text{ox}}$ ) and L is the length of the MoS<sub>2</sub> channel. With an estimation of  $R_{\text{th}}$ , the increase in temperature can be expressed as:

$$T_{\text{avg}} = T_0 + PR_{\text{th}} \left\{ \frac{1 + gL_H R_T x - 2xL_H / L}{1 + gL_H R_T x} \right\}$$

(E11)